## Low-frequency noise behavior of tunneling field effect transistors

J. Wan, <sup>1,a)</sup> C. Le Royer, <sup>2</sup> A. Zaslavsky, <sup>1,3</sup> and S. Cristoloveanu <sup>1</sup>

<sup>1</sup>IMEP-LAHC, INP-Grenoble, MINATEC, 3 Parvis Louis Neel, BP 257, 38016 Grenoble, France <sup>2</sup>CEA-LETI, MINATEC, 17 Avenue des Martyrs, 38054 Grenoble Cedex 9, France <sup>3</sup>School of Engineering, Brown University, Providence, Rhode Island 02912, USA

(Received 2 November 2010; accepted 16 November 2010; published online 14 December 2010)

We report on the low-frequency noise (LFN) properties of tunneling field effect transistors (TFETs) fabricated on silicon-on-insulator substrate. Unlike conventional large FETs, where LFN obeys a 1/f frequency dependence, in large TFETs the LFN is dominated by random telegraph signal (RTS) noise characterized by  $1/f^2$  slope. We explain this unique LFN behavior by the local junction control of the tunneling drain current, which involves few traps in a small area. The origin of RTS noise is corroborated by the gate length independence of the  $I_D$ - $V_{GS}$  characteristics of TFETs. The relatively high amplitude of RTS noise in TFETs will have circuit design implications. © 2010 American Institute of Physics. [doi:10.1063/1.3526722]

The downscaling of conventional complementary metaloxide-semiconductor (CMOS) devices has yielded faster and cheaper circuits over the past decades. One of the impediments to further downscaling is the emergence of shortchannel effects (SCEs) that increase the subthreshold slope (S) and transistor off current ( $I_{off}$ ). The fully depleted (FD) and multigate MOS field effect transistors (MOSFETs) based on silicon-on-insulator (SOI) substrates have been implemented to enhance gate controllability, thus mitigating the SCEs. However, the S in standard MOSFETs cannot reach below 2.3(kT/q). As a result, alternative devices based on conventional semiconductor materials and processes are of interest. Among these, the tunneling field effect transistor<sup>1</sup> (TFET) is interesting due to its promise of low I<sub>off</sub> and S, which could potentially reduce the supply voltage and hence the power consumption below the standard MOSFET limits. TFETs with S<60 mV/decade at room temperature have been demonstrated experimentally, albeit with relatively low on currents (I<sub>on</sub>).<sup>2-5</sup> Recently, most of the studies on TFETs have concentrated on enhancing the  $I_{\rm on}$  using low-bandgap materials such as germanium (Ge), <sup>6,7</sup> III–V compounds, <sup>8</sup> carbon nanotubes, <sup>9</sup> and even graphene. <sup>10,11</sup> Other important aspects of TFETs, such as noise, have received less attention.

In this letter, we present low-frequency noise (LFN) measurements on TFETs fabricated in parallel with MOSFETs on FD SOI substrates using an advanced CMOS process. We observed random telegraph signal (RTS) noise with  $1/f^2$  slope even in large TFETs. The RTS current noise in TFETs also shows amplitude as high as 5% and large device to device variability. This is different from large MOSFETs in which the 1/f noise is dominant. We attribute the strikingly different LFN properties of TFETs and similarly sized MOSFETs to the extremely small section of gate overlapping the narrow tunneling junction that actually controls the current in TFETs.

The LFN of standard MOSFETs is an important limiting factor in analog and digital circuits. <sup>12,13</sup> Since the LFN-generating mechanism is the trapping at the channel-gate dielectric interface, MOSFET LFN measurements are also

used to extract the density and energy distribution of the interface traps.  $^{14-19}$  As TFET technology matures, LFN properties of TFETs will also impact circuit functionality. But even at the single device level, the  $1/f^2$  LFN dependence in TFETs provides a useful experimental signature distinguishing the tunneling current mechanism from standard MOSFET current

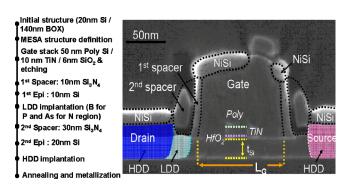

The fabrication process flows of TFETs and FD-SOI MOSFETs are totally compatible, as illustrated in Fig. 1. The process started from a SOI substrate with 140 nm buried oxide and 20 nm active Si layer. The isolated device active areas (mesa structures) are formed by photolithography and dry etching, followed by the definition and etching of the gate stack consisting of a 6 nm SiO<sub>2</sub> gate oxide, a 10 nm TiN metal gate, and 50 nm of polysilicon. The first spacer is formed by the deposition of 10 nm Si<sub>3</sub>N<sub>4</sub>. The lightly doped drain (LDD) is formed for the MOSFETs and TFETs in different ways by altering the lithographic mask. For N-type LDD implantation, the window is opened on both the source and drain sides of NMOSFETs and only on the drain side of TFETs, and then implanted with As at 9 keV with a dose of  $1 \times 10^{15}$  cm<sup>-2</sup>. For P-type LDD implantation, the window is opened on both the source and drain sides of PMOSFETs and only at the source side of TFETs, and implanted with BF2 at 7 keV with a dose of  $1 \times 10^{15}$  cm<sup>-2</sup>. Then, a second spacer of 15 or 30 nm and a Si layer of 20 nm were deposited

FIG. 1. (Color online) Fabrication process flow and SEM cross-section of the FD-SOI TFETs. The fabrication follows the standard MOSFET process with double spacers to lower the parasitic capacitance and raised source/drain to reduce the series resistance.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: wanj@minatec.inpg.fr.

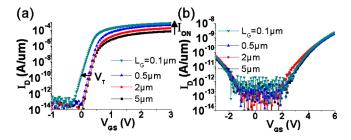

FIG. 2. (Color online) Measured  $I_D\text{-}V_{GS}$  characteristics ( $V_{DS}\text{=}1~V$ ) of (a) MOSFETs and (b) TFETs with  $L_G$  decreasing from 5  $\,\mu\text{m}$  to 100 nm. The  $I_{on}$  of MOSFETs tends to increase as  $L_G$  decreases and  $V_T$  decreases due to short-channel effects. The  $I_D$  of TFETs remains stable even when  $L_G$  decreases to 100 nm.

(raised source and drain for reduced series resistance). The heavily doped drain (HDD) implantation followed the same process as LDD except that the As dose and energy for NHDD implantation were  $2\times10^{15}~{\rm cm^{-2}}$  and 20 keV, respectively, whereas for BF $_2$  PHDD implantation these values were  $3\times10^{15}~{\rm cm^{-2}}$  and 5 keV. Rapid thermal annealing was used to activate the dopants, followed by the back-end process.

The structure of our TFETs is analogous to that of a MOSFET with double spacers and raised source/drain regions, as shown in Fig. 1, with the only structural difference lying in the opposite doping of the TFET source and drain.

Figure 2 compares the  $I_D$ - $V_{GS}$  characteristics of NMOS-FETs and NTFETs with different gate lengths ( $L_G$ ) from 5  $\mu$ m to 100 nm. The  $I_{on}$  of TFETs is almost 5–6 decades lower than that of MOSFETs due to the large bandgap of silicon and the insufficiently abrupt tunnel junction. As can be seen from Fig. 2(a), in MOSFETs the  $I_{on}$  increases as  $L_G$  decreases due to larger channel conductance. As  $L_G$  decreases to 100 nm, the threshold voltage ( $V_T$ ) of the NMOSFET tends to decrease due to the drain induced barrier lowering (DIBL). In TFETs, neither the  $I_{on}$  nor  $V_T$  changes as  $L_G$  decreases from 5  $\mu$ m to 100 nm. This indicates that the current in TFETs is not controlled by channel conductance as in MOSFETs, but by interband tunneling at the source-

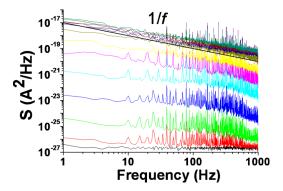

FIG. 3. (Color online) LFN spectra of NMOS (LG=350 nm, W=10  $\mu m,$   $V_{DS}\!=\!50$  mV, and  $V_{GS}\!=\!0.1\!-\!1.5$  V).

channel junction, which is also confirmed by the weak temperature dependence of  $I_D$ . Therefore, the characteristics of TFETs are independent of  $L_G$ , at least for the low  $I_{on}$  levels demonstrated thus far.

In MOSFETs, the LFN is mainly caused by the fluctuation of the channel carrier density due to the trapping-detrapping process at the channel-dielectric interface. A single trapping-detrapping event causes RTS noise with Lorentzian spectrum characterized by  $1/f^2$  slope. <sup>14,16</sup> For MOSFETs with large gate area, the superposition of many trapping-detrapping events produces 1/f noise, see Fig. 3. As the gate area of MOSFETs decreases below 1  $\mu$ m<sup>2</sup>, only one or a few near-interface oxide traps exist in the entire device, leading to RTS current noise.

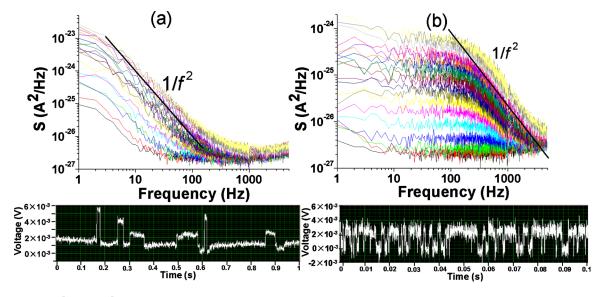

Figure 4 shows the spectrum of two NTFETs with the same 6 nm  $SiO_2$  gate oxide presenting totally different spectral behavior. In the NMOSFET of Fig. 3 with a gate area of 3.5  $\mu$ m<sup>2</sup> (L<sub>G</sub>=350 nm) the LFN is 1/f, whereas in the NTFETs the noise spectrum is Lorentzian with  $1/f^2$  slope despite the much larger 25  $\mu$ m<sup>2</sup> gate area (L<sub>G</sub>=5  $\mu$ m). The lower images in Fig. 4 show the output voltage of the amplifier used for detecting the fluctuation in  $I_D$ . The sensitivity of the amplifier is  $1 \times 10^{-8}$  A/V which indicates that the maximum fluctuation in  $I_D$  is  $\sim$ 5% in the TFET of Fig. 4(a).

FIG. 4. (Color online) [(a) and (b)] LFN spectra of two NTFETs with the same structure and bias ( $L_G=5~\mu m$ ,  $V_{DS}=1~V$ , and  $V_{GS}=3-5~V$ ). The lower images show the time variation of the output voltage from the amplifier used to capture the LFN signal in the NTFET. The RTS noise can be clearly observed with an amplitude of  $\sim 0.003~V$  (output voltage)  $\times 10^{-8}~A/V$  (amplifier sensitivity)= $3\times 10^{-11}~A$  for the NTFET in (a). RTS of lower amplitude and higher characteristic frequency is observed in (b), indicating large variability due to single-trap events.

In TFETs, the same trapping-detrapping process occurs at the Si-SiO2 interface as in MOSFETs. However, the impact of this process depends on the location of the traps. First, the trapping can modulate the channel conductance, just as in a MOSFET, but as we have discussed already, the fluctuations in the channel conductance have a negligible effect on I<sub>D</sub>. Second, the trapping-detrapping events near the tunneling junction can change the maximum junction electric field  $F_{\text{max}}$ , causing fluctuations in the interband tunneling rate which is exponentially dependent on  $F_{\text{max}}$ . The corresponding area is determined by the detailed structure and gate/drain bias of TFET, but it is generally very narrow (<10 nm).<sup>21</sup> Hence, the effective LFN-generating area of the TFET is very small ( $<0.05 \mu m^2$  for device width W =5  $\mu$ m), including only discrete numbers of traps, just as in a very small MOSFET. This is why the RTS noise is observed in TFETs even if the gate area is nominally large.

As in small MOSFETs, <sup>16</sup> the RTS noise in TFETs is

As in small MOSFETs, <sup>10</sup> the RTS noise in TFETs is characterized by a large variability. The TFET in Fig. 4(a) exhibits RTS caused by two or three traps that cause different I<sub>D</sub> jumps at different trapping rates. The TFET in Fig. 4(b), which has nominally the same structure and dimension, includes a single RTS-generating trap with lower RTS amplitude. The trapping-detrapping process is also faster, resulting in a much higher characteristic frequency.

Due to its extremely small effective gate length (<10 nm), the amplitude of RTS noise in our TFETs is comparable to that in very small MOSFETs, <sup>15</sup> even though the transconductance is much lower. However, as TFET performance is enhanced by the introduction of alternative low-bandgap materials (Ge) and more effective electrostatic modulation of tunneling junction electric field, we can expect that RTS noise will become a major issue for the TFET-based circuits of the future.

In conclusion, we have measured the LFN characteristics of TFETs fabricated in parallel with FD-SOI MOSFETs on the same wafer. By comparing the  $\rm I_D\text{-}V_{GS}$  and noise characteristics of TFETs and MOSFETs, we confirm that the current in TFETs is controlled by the tunneling junction and is independent of  $\rm L_G$ . Our LFN measurements reveal that, unlike in MOSFETs, the RTS noise with  $1/f^2$  frequency dependence and large amplitude variability is dominant in TFETs even though the nominal gate area is large because the rel-

evant area where the interband tunneling takes place is much smaller than the physical  $L_G$ .

The work at Minatec is funded by the RTRA program of the Grenoble Nanosciences Foundation. One of the authors (A.Z.) also acknowledges support by the U.S. National Science Foundation (Award No. ECCS-0701635).

<sup>1</sup>W. M. Reddick and G. A. J. Amaratunga, Appl. Phys. Lett. **67**, 494 (1995).

<sup>2</sup>W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, IEEE Electron Device Lett. 28, 743 (2007).

<sup>3</sup>F. Mayer, C. Le Royer, J.-F. Damlencourt, K. Romanjek, F. Andrieu, C. Tabone, B. Previtali, and S. Deleonibus, Tech. Dig. - Int. Electron Devices Meet. **2008**, 163.

<sup>4</sup>T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, Tech. Dig. - Int. Electron Devices Meet. **2008**, 947.

<sup>5</sup>S. H. Kim, H. Kam, C. Hu, and T.-J. K. Liu, Dig. Tech. Pap. - Symp. VLSI Technol. **2009**, 178.

<sup>6</sup>D. Kazazis, P. Jannaty, A. Zaslavsky, C. Le Royer, C. Tabone, L. Clavelier, and S. Cristoloveanu, Appl. Phys. Lett. **94**, 263508 (2009).

<sup>7</sup>O. M. Nayfeh, J. L. Hoyt, and D. Antoniadis, IEEE Trans. Electron Devices **56**, 2264 (2009).

<sup>8</sup>K. Ganapathi, Y. Yoon, and S. Salahuddin, Appl. Phys. Lett. **97**, 033504 (2010).

<sup>9</sup>J. Appenzeller, Y. M. Lin, J. Knoch, and Ph. Avouris, Phys. Rev. Lett. **93**, 196805 (2004).

G. Fiori and G. Iannaccone, IEEE Electron Device Lett. 30, 1096 (2009).

Y. Gao, T. Low, and M. Lundstrom, Dig. Tech. Pap. - Symp. VLSI Technol. 2009, 180.

<sup>12</sup>S. R. Li, Y. L. R. Lu, W. McMahon, Y. H. Lee, and N. Mielke, Dig. Tech. Pap. - Symp. VLSI Technol. **2007**, 56.

<sup>13</sup>P. Fantini, A. Ghetti, A. Marinoni, G. Ghidini, A. Visconti, and A. Marmiroli, IEEE Electron Device Lett. **28**, 1114 (2007).

<sup>14</sup>F. N. Hooge, T. G. M. Kleinpenning, and L. K. J. Vandamme, Rep. Prog. Phys. 44, 479 (1981).

<sup>15</sup>T. Boutchacha and G. Ghibaudo, Phys. Status Solidi A 167, 261 (1998).

<sup>16</sup>G. Ghibaudo and T. Boutchacha, Microelectron. Reliab. **42**, 573 (2002).

<sup>17</sup>J. Zhuge, R. S. Wang, R. Huang, Y. Tian, L. L. Zhang, D. W. Kim, D. Park, and Y. Y. Wang, IEEE Electron Device Lett. 30, 57 (2009).

<sup>18</sup>Y. Xu, T. Minari, K. Tsukagoshi, R. Gwoziecki, R. Coppard, F. Balestra, J. A. Chroboczek, and G. Ghibaudo, Appl. Phys. Lett. **97**, 033503 (2010).

<sup>19</sup>D. Y. Jang, J. W. Lee, K. Tachi, L. Montes, T. Ernst, G. T. Kim, and G. Ghibaudo, Appl. Phys. Lett. **97**, 073505 (2010).

<sup>20</sup>J. Wan, C. Le Royer, A. Zaslavsky, and S. Cristoloveanu, European Solid-State Device Research Conference (ESSDERC), 2010, pp. 341–344.

<sup>21</sup>C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, and S. Deleonibus, Appl. Phys. Lett. 84, 1780 (2004).

<sup>22</sup>E. O. Kane, J. Appl. Phys. **32**, 83 (1961).