Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Tunneling FETs on SOI: Suppression of ambipolar leakage, low-frequency noise behavior, and modeling

J. Wan <sup>a,\*</sup>, C. Le Royer <sup>b</sup>, A. Zaslavsky <sup>c</sup>, S. Cristoloveanu <sup>a</sup>

- <sup>a</sup> IMEP-LAHC, INP-Grenoble, MINATEC, 3 Parvis Louis Neel, BP 257, 38016 Grenoble, France

- <sup>b</sup> CEA-LETI, MINATEC, 17 Avenue des Martyrs, 38054 Grenoble Cedex 9, France

#### ARTICLE INFO

Article history: Available online 6 August 2011

Keywords: Tunneling Field effect transistor Ambipolar leakage Analytical model Low frequency noise

#### ABSTRACT

We report on thin-body tunneling field-effect transistors (TFETs) built on SOI substrates with both  $SiO_2$  and  $HfO_2$  gate dielectrics. The source–drain leakage current is suppressed by the introduction of an intrinsic region adjacent to the drain, reducing the electric field at the tunnel junction in the off state. We also investigate the temperature dependence of the TFET characteristics and demonstrate that the temperature-induced change in the Si bandgap is the main mechanism that determines the tunneling barrier and hence the drain current  $I_D$ . We present a model of the TFET as a combination of a gated diode and a MOSFET, which can be solved analytically and can predict the experimentally measured  $I_D$  over a wide range of drain and gate bias. Finally we report on the low frequency noise (LFN) behavior of TFETs, which unlike conventional MOSFETs exhibits  $1/J^2$  frequency dependence even for large gate areas. This dependence indicates less trapping due to the much smaller effective gate length over the tunneling junction.

## 1. Introduction

As the scaling of conventional CMOS devices is hampered by short-channel effects (SCEs), silicon-compatible devices based on different principles are being studied for their unique properties. In particular, the tunneling field effect transistor (TFET) [1] is of interest due to its complete semiconductor process compatibility and similarity of device layout with the Si MOSFET. The current in TFETs is carried by band-to-band tunneling (BTBT), which makes it theoretically possible to reach extremely low off-state currents  $(I_{OFF})$  as well as an ultra-low subthreshold slope (S) below the ideal MOSFET value of 60 mV/decade at room temperature. A number of studies have focused on power consumption in TFETs, reporting a theoretical advantage over standard MOSFETs [2,3]. In order to enhance the on-state current ( $I_{ON}$ ), multigate [4] and lower bandgap semiconductors, such as Ge and SiGe, have been reported [5-9]. At the same time, experimentally realized TFETs have typically suffered from difficulties in simultaneously achieving low S and high  $I_{ON}$ , as well as from high source-drain leakage current ( $I_{LEAK}$ ) due to ambipolar conduction, especially for low bandgap semiconductors.

In addition to experimental demonstrations, analytical TFET models are important for understanding device physics (including

BTBT and leakage effects) and quick prediction of device performance [10–12]. In previously reported models, the channel was assumed to be fully depleted, which suppresses [11] or minimizes [12] the effect of drain voltage  $V_{\rm D}$  on the tunneling junction, especially at high gate voltage  $V_{\rm GS}$  in long-channel TFETs. Furthermore, ignoring the carrier transport in the channel also removes the current saturation mechanism of future TFETs with higher  $I_{\rm ON}$ .

In this work, we focus on several aspects of Si TFETs. First, we compare TFETs with SiO<sub>2</sub> and HfO<sub>2</sub> gate dielectrics to demonstrate lower S and higher  $I_{ON}$  in devices with thinner equivalent oxide thickness (EOT). Second, an asymmetrical TFET layout with an intrinsic region  $(L_{IN})$  at drain side is demonstrated to effectively suppress  $I_{LEAK}$  while retaining the same  $I_{ON}$ . These experimental results are confirmed using device and process simulations based on Silvaco TCAD. Third, temperature variation tests are performed to examine the validity of Kane's model [13] of the BTBT process. Further, an analytical model of TFET including a MOSFET channel component is proposed. While this model requires numerical evaluation over the entire range of bias and current, it reduces to a compact and convenient form for our experimental TFETs with relatively low  $I_{ON}$ . Finally, we present low-frequency noise (LFN) measurements on TFETs and qualitatively explain the different LFN properties of TFETs compared to standard MOSFETs (where LFN measurements are widely used to extract trap properties [14,15]).

<sup>&</sup>lt;sup>c</sup> School of Engineering, Brown University, Providence, RI 02912, USA

<sup>\*</sup> Corresponding author.

E-mail address: wanj@minatec.inpg.fr (J. Wan).

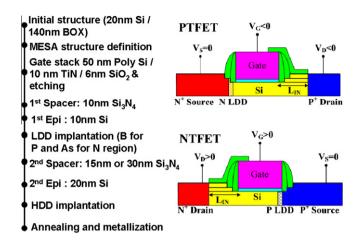

**Fig. 1.** Fabrication process flow and bias polarity of TFETs. In PTFET, the gate is negatively biased and the BTBT occurs at the n+ doped source. Conversely, in NTFET, the gate is positively biased and the BTBT occurs at the p+ doped source.

#### 2. Fabrication and device structure

#### 2.1. Fabrication process

Our TFET fabrication sequence is completely compatible with fully depleted SOI CMOS process flow. The process started from an SOI Unibond substrate with 140 nm BOX and 20 nm active Si layer. The isolated device active areas (mesa structure) were formed by photolithography and dry etching, followed by the definition of gate stack which is composed of three layers, as illustrated in Fig. 1. Two different gate oxides were formed for comparison: either a 6 nm SiO<sub>2</sub> grown by dry oxidation or a 3 nm ALD-deposited HfO<sub>2</sub>. After the deposition of a metal gate (10 nm TiN), 50 nm thick polysilicon was deposited for silicidation. The first spacer was formed by the deposition of 10 nm Si<sub>3</sub>N<sub>4</sub> in LPCVD, then a 10 nm Si laver was epitaxially grown by CVD process. The N-type LDD was formed by implantation of As with dose of  $1 \times 10^{15}$  cm<sup>-2</sup> and energy of 9 keV, while BF<sub>2</sub> implantation with dose of  $1 \times 10^{15}$  cm<sup>-2</sup> and energy of 7 keV was used for formation of P-type LDD. Then, a second spacer of 15 or 30 nm and a Si layer of 20 nm were deposited. Before the implantation of N-HDD and P-HDD regions, a Si<sub>3</sub>N<sub>4</sub> layer was formed to protect the intrinsic region  $L_{IN}$ . The dose and energy of As for NHDD implantation were  $2 \times 10^{15} \, \text{cm}^{-2}$  and 20 keV, respectively, whereas, for PHDD implantation, these values were  $3 \times 10^{15}$  cm<sup>-2</sup> and 5 keV. Rapid thermal annealing (RTA) was used to activate the dopants, followed by the metallization.

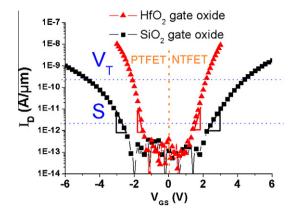

**Fig. 3.** Measured  $I_D$ – $V_{CS}$  curves of both NTFETs and PTFETs based on different gate oxides ( $L_G$  = 400 nm,  $|V_{DS}|$  = 1 V). The inset symbols show the definitions of  $V_T$  and S.

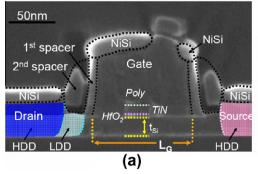

#### 2.2. Device structure

The structure of the fabricated TFETs is quite similar to that of a MOSFET with double spacers and raised S/D, shown in Fig. 2a. The only structural difference between TFETs and MOSFETs lies in the opposite doping of the TFET source and drain. Furthermore, for suppressing the ambipolar current, the structure of some TFETs was rendered asymmetrical by adding an intrinsic region  $L_{\rm IN}$  separating the drain contact from the channel as shown in Fig. 2b.

For simplicity, the N+ region in a PTFET is defined as source while the P+ region is defined as drain. The opposite definition applies to NTFETs, as shown in Fig. 1. The source of both PTFETs and NTFETs is always grounded, while the drain is negatively biased in PTFETs and positively biased in NTFETs. The  $I_{\rm ON}$  is produced by tunneling at the source-channel junction at  $V_{\rm GS} < 0$  for PTFETs and  $V_{\rm GS} > 0$  for NTFETs.

#### 3. Electrical characterization and analysis

The fabricated devices were systematically characterized. From C–V measurements, the EOT values of TFETs with 6 nm  $SiO_2$  and 3 nm  $HfO_2$  gate oxides were 6 nm and 2.2 nm, respectively. The gate width of all TFETs was 10  $\mu$ m, the gate length  $L_G$  varied from 100 to 400 nm, and the intrinsic region length  $L_{IN}$  varied from 0 to 100 nm.

#### 3.1. Impact of gate oxide on characteristics

A comparison of  $I_{\rm D}$ – $V_{\rm GS}$  curves of NTFETs and PTFETs with different gate oxides and  $L_{\rm G}$  = 400 nm and  $|V_{\rm D}|$  = 1 V is shown in

Fig. 2. SEM images of fabricated conventional (a) and asymmetric (b) TFETs.

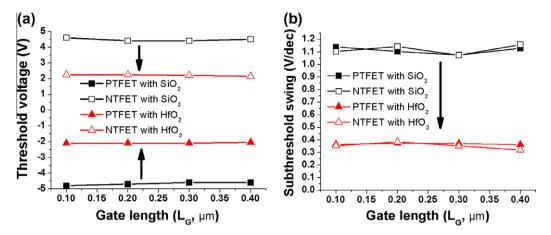

**Fig. 4.** Comparison of  $V_T$  (a) and S (b) values of the TFETs with different gate oxide and gate length.

Fig. 3. In TFETs, there exists no unambiguous definition of threshold voltage  $V_{\rm T}$  and S is not a constant value. For comparison purposes, we define the  $V_{\rm T}$  as the voltage when  $I_{\rm D}$  equals  $2\times 10^{-10}\,{\rm A/\mu m}$  and extract the S value when  $I_{\rm D}$  reaches  $2\times 10^{-12}\,{\rm A/\mu m}$ , ranging over two decades in drain current. As can be easily observed in Fig. 3, TFETs with HfO<sub>2</sub> gate oxide have smaller  $V_{\rm T}$  and higher  $I_{\rm ON}$  than those based on SiO<sub>2</sub>. The S values are also markedly reduced.

As described in Fig. 4, the results on devices with different  $L_{\rm G}$  = 100–400 nm show that  $V_{\rm T}$  and S are independent of  $L_{\rm G}$ . This is due to the fact that at low  $I_{\rm D}$  the tunneling current is determined by the maximum electric field at the tunneling junction and unaffected by the carrier transport in the channel [16]. Fig. 4a shows that  $V_{\rm T}$  is 4.5 V for both NTFETs and PTFETs with SiO<sub>2</sub>, whereas  $V_{\rm T}$  is 2.3 V for those with HfO<sub>2</sub> gate oxide. As for the S value, shown in Fig. 4b, both NTFETs and PTFETs with SiO<sub>2</sub> have  $S \sim 1.1$  V/decade, which is reduced to 0.33 V/decade in devices with HfO<sub>2</sub>. We note that one wafer (with HfO<sub>2</sub> gate oxide) from this lot yielded remarkably low S [5] for reasons that are still under investigation. Here, we only focus on a comparison of identically processed devices with different dielectrics.

The comparison reveals that thinner EOT can lead to lower  $V_{\rm T}$  and S values due to the better electrostatic controllability from the gate. The theoretically achievable S < 60 mV/decade value in TFETs requires excellent electrostatic control of the maximum junction field, which implies minimizing gate EOT and sharpening the S/D lateral doping profile. As a result, the experimental reports of low S published thus far [5,7,17] have generally suffered from low  $I_{\rm ON}$ , at least for reasonable  $V_{\rm D}$  values.

#### 3.2. Impact of device architecture on characteristics

A potential problem of symmetrical TFETs is the large  $I_{\rm LEAK}$  under opposite gate bias, because interband tunneling can occur at either the source-channel or the drain-channel junction depending on the sign of  $V_{\rm GS}$ . This ambipolar  $I_{\rm LEAK}$  can be more severe for TFETs based on low bandgap semiconductors, such as Ge. The solution is to introduce an asymmetrical architecture, such as unequal source/drain doping [7,18], intrinsic regions and lateral heterojunctions [7,9].

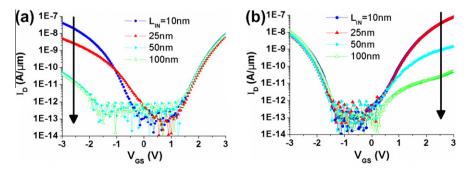

Among these solutions, the introduction of intrinsic region is the simplest, requiring an easy change in the photomask, as shown in the inset of Fig. 2b. This method was originally proposed in a simulation paper [19]; the first experimental data have been presented in [5]. Here, we present a systematic study by the combination of simulation and experiment. We also demonstrate the possibility of completely suppressing the ambipolar  $I_{\text{LEAK}}$ . Fig. 5

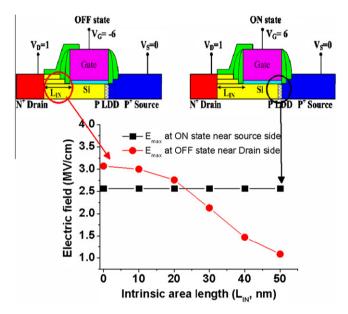

**Fig. 5.** The maximum electric field ( $E_{\rm max}$ ) at the tunneling junction of a NTFET with different  $L_{\rm IN}$  under positive gate bias and negative gate bias.

shows a NTFET with intrinsic region operated under different  $V_{\rm GS}$  and its corresponding simulated maximum electric field ( $E_{\rm max}$ ) at the tunneling junction. Under positive gate bias, the TFET is in the ON state and the tunneling occurs at source side. The  $E_{\rm max}$  at the source side is almost constant as  $L_{\rm IN}$  increases due to the negligible potential drop on  $L_{\rm IN}$  region, see Fig. 5.

In contrast, as the gate is negatively biased, the TFET is in OFF state and the tunneling occurs at drain side where the intrinsic area is located. For the TFET with  $L_{\rm IN}$  smaller than 20 nm, the  $E_{\rm max}$  in the off state is even slightly larger than in the ON state, see Fig. 5. However, as  $L_{\rm IN}$  increases beyond 20 nm, the  $E_{\rm max}$  at the drain side falls quickly. Since the BTBT rate is exponentially dependent on  $E_{\rm max}$  it can be suppressed at the drain side by increasing  $L_{\rm IN}$ . However, at the source side, the  $E_{\rm max}$  does not change, so  $L_{\rm IN}$  does not degrade  $I_{\rm ON}$ .

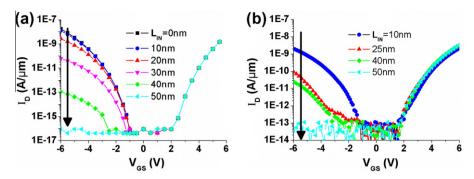

A comparison of the simulated and experimental results for an NTFET with different values of  $L_{\rm IN}$  is shown in Fig. 6, where the simulated tunneling current in Fig. 6a is obtained from Kane's model as discussed below. As expected, the simulated  $I_{\rm LEAK}$  of the NTFET with  $L_{\rm IN} \leqslant 20$  nm is comparable to the  $I_{\rm ON}$  due to the large  $E_{\rm max}$ , but it can be markedly suppressed by increasing  $L_{\rm IN}$  to 50 nm.

Fig. 6.  $I_D$ - $V_{CS}$  curves of NTFETs with SiO<sub>2</sub> gate oxide and different  $L_{IN}$  at  $V_{DS}$  = 1 V from simulation (a) and experiment (b), all devices have  $L_G$  = 400 nm.

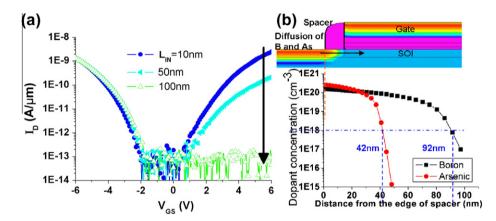

Fig. 7.  $I_D$ - $V_{GS}$  curve of PTFETs with SiO<sub>2</sub> gate oxide and different  $L_{IN}$  (a) and the simulation of the lateral diffusion profiles of boron and arsenic dopants (b). The dotted line indicates the boundary for suppressing the tunneling current.

Fig. 6b shows the experimental results for NTFETs with four different  $L_{\rm IN}$  from 0 to 50 nm. Again, in agreement with the simulation, the  $I_{\rm LEAK}$  of the TFETs without  $L_{\rm IN}$  is comparable to  $I_{\rm ON}$ , but can be effectively suppressed by increasing  $L_{\rm IN}$  to 50 nm.

In PTFETs, the  $I_{\rm ON}$  is also unaffected by  $L_{\rm IN}$ , as can be seen in Fig. 7a. However, the full suppression of  $I_{\rm LEAK}$  in PTFETs requires a larger  $L_{\rm IN}$  = 100 nm. We attribute this difference to the different diffusion coefficients of boron (B) and arsenic (As) in Si. Fig. 7b shows the simulated doping profiles of implanted B and As after the activation anneal. All parameters in simulation were adjusted according to the fabrication process. As previous work indicates [14], a doping concentration which is lower than  $1\times 10^{18}\,{\rm cm}^{-3}$  can be used to effectively suppress the tunneling. In our case, the  $I_{\rm LEAK}$  results from the tunneling at drain side which is doped by As and B in NTFETs and PTFETs, respectively. The characteristic diffusion distance from the edge of spacer to the  $10^{18}\,{\rm cm}^{-3}$  value

point is  $\sim$ 40 nm for As and  $\sim$ 90 nm for B, as shown in Fig. 7b, qualitatively explaining our experimental observations.

The same tendency applies to TFETs with  $HfO_2$  gate oxide and smaller EOT. As shown in Fig 8a, the  $I_{LEAK}$  of  $HfO_2$  based NTFETs drops rapidly as  $L_{IN}$  increases. Note that the residual  $I_{LEAK}$  as  $L_{IN}$  exceeds 50 nm is caused by gate leakage, which cannot be suppressed by  $L_{IN}$ . However, for  $HfO_2$ -based PTFETs,  $L_{IN}$  as long as 100 nm reduces the  $I_{LEAK}$  but cannot completely suppress it, due to both the effects of the longer B diffusion length and stronger gate control of  $E_{max}$ , see Fig. 8b.

#### 3.3. Impact of temperature on characteristics

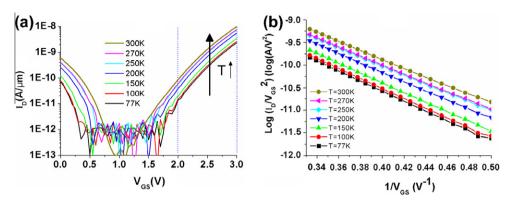

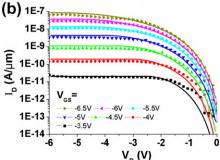

Fig. 9a shows the  $I_{\rm D}$ – $V_{\rm GS}$  of a NTFET with HfO<sub>2</sub> gate oxide,  $L_{\rm G}$  = 400 nm and  $L_{\rm IN}$  = 10 nm at temperatures ranging from 77 to 300 K. At low  $I_{\rm D}$ , where the current is dominated by the interband

**Fig. 8.**  $I_D$ – $V_{GS}$  curves of NTFETs (a) and PTFETs (b) with HfO<sub>2</sub> gate oxides and different  $L_{IN}$ .

**Fig. 9.** (a)  $I_D$ – $V_{GS}$  characteristics and (b)  $\log(I_D/V_{GS}^2) - V_{GS}^{-1}$  curves at  $V_{DS} = 1$  V for an NTFET with  $L_G = 400$  nm as a function of temperature T.

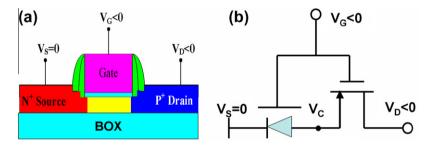

**Fig. 10.** (a) Schematic view of a TFET operating in P mode with  $V_{GS} < 0$  biased sufficiently low to create a hole inversion channel under the gate. (b) The proposed model of the PTFET as a series combination of a gate-controllable source-channel tunnel diode with a PMOSFET.

tunneling at the source-channel junction, the temperature dependence of the TFET  $I_D$  can be qualitatively explained by the Kane tunneling model [13]:

$$I_{\rm D} = A_{\rm K} \cdot E_{\rm max}^2 \cdot \exp\left(-\frac{B_{\rm K}}{E_{\rm max}}\right)$$

with  $E_{\rm max} \propto V_{\rm GS}$  and  $B_{\rm K} \propto E_{\rm G}^{\frac{3}{2}}$  (1)

where  $A_K$ ,  $B_K$  are tunneling parameters which depend on the bandgap and carrier effective mass in the channel material. The dominant temperature effect on the TFETs performance comes from the temperature variation of bandgap  $E_G$ , which enters in the exponential of Eq. (1). In Si,  $E_G$  has weakly negative temperature dependence [20]:

$$E_{\rm G}(T) = E(0) - \frac{\alpha \cdot T^2}{T + \beta} \tag{2}$$

As temperature increases, the  $E_{\rm G}$  decreases, leading to a corresponding decrease in parameter  $B_{\rm K}$  and hence an increasing tunneling current.

The validity of Kane's model can be examined by rewriting Eq. (1) as:

$$\log\left(\frac{I_{\rm D}}{V_{\rm GS}^2}\right) \propto -\frac{B_{\rm K}}{V_{\rm GS}} \tag{3}$$

Fig. 9b confirms the linear relationship between  $\log(I_{\rm D}/V_{\rm GS}^2)$  and  $1/V_{\rm GS}$  over the entire temperature range. The slight variation in the slope reflects the increase of the  $B_{\rm K}$  coefficient at low temperature. Since the temperature dependence of TFET  $I_{\rm D}$  agrees with that reported previously [5] and with Eq. (1), we can drawn two main conclusions:

(i) The weak temperature dependence of the drain current  $I_{\rm D}$  confirms that BTBT is the dominant mechanism in TFETs. By contrast, the drain current in MOSFETs is strongly temperature-dependent, mainly due to mobility variation.

(ii) The Kane model is at least qualitatively effective in describing the BTBT process in Si TFETs.

#### 3.4. TFET model combining tunneling junction and channel transport

A schematic picture of a biased PTFET working is shown in Fig. 10a. At sufficiently negative  $V_{\rm GS}$ , a hole layer is induced in the channel, creating a reverse-biased tunneling junction between the source and the channel. The tunneling junction is formed at the source side as a reverse biased P–N diode. We can model the resulting device as the series connection of a PMOSFET channel with a gate-controlled tunnel diode at the source-channel junction, as shown in Fig. 10b. The PMOSFET has a well defined  $V_{\rm D}$  at the drain, but its source coincides with the cathode of the tunneling diode and is at a bias  $V_{\rm C}$  determined by current continuity.

Because of the nonlinear equations describing the  $I_{\rm D}(V_{\rm GS},V_{\rm D}-V_{\rm C})$  of the MOSFET and the  $I_{\rm D}(V_{\rm GS},V_{\rm C})$  tunneling current of the gated diode, a general solution can only be obtained numerically. However, at the relatively low tunneling  $I_{\rm D}$  observed in our TFETs, we can simplify our model by considering the MOSFET to be either in the linear or the saturation regimes, leading to two possible values of  $V_{\rm C}$ :

$$V_{\rm C} = V_{\rm D}$$

if  $|V_{\rm D}| < |V_{\rm GS} - V_{\rm th}|$  (linear region) or  $V_{\rm C} = V_{\rm GS} - V_{\rm th}$  if  $|V_{\rm D}| > |V_{\rm GS} - V_{\rm th}|$  (saturation region) (4)

where  $V_{\rm th}$  is the threshold voltage of the MOSFET channel (not the same as the  $V_{\rm T}$  of the TFET discussed in Section 2). In linear region of the MOSFET,  $V_{\rm C}$  follows  $V_{\rm D}$  and the tunneling diode current depends both on  $V_{\rm GS}$  and  $V_{\rm D}$ . On the other hand, when  $|V_{\rm D}| \geqslant |V_{\rm GS} - V_{\rm th}|$  and the MOSFET is saturated,  $V_{\rm C}$  becomes a function of  $V_{\rm GS}$  only and the tunneling current  $I_{\rm D}$  ( $V_{\rm GS}$ ,  $V_{\rm C}$ ) becomes independent of  $V_{\rm D}$ .

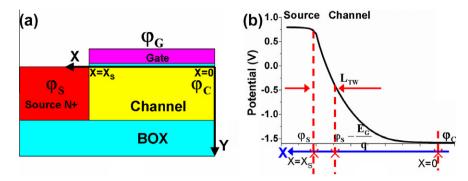

Fig. 11. (a) Schematic view of the tunneling junction in which the potential distribution is decided by the potentials of the gate  $φ_G$ , source  $φ_S$  and channel  $φ_C$ . (b) Potential profile along the tunneling junction obtained from TCAD simulation showing the shortest tunneling width  $L_{TW}$  between the source at potential  $φ_S$  and the point at the potential  $(φ_S - E_G/q)$ .

We can obtain an expression for  $I_D(V_{GS},V_C)$  of the gate-controlled tunneling diode by solving the potential profile around the tunneling junction, shown in Fig. 11a, using the pseudo-2D Poisson equation approach described previously [12,21]. The surface potential along the tunneling direction can be defined in terms of the electrostatic potentials of gate  $(\varphi_G)$ , source  $(\varphi_S)$ , and channel  $(\varphi_C)$ , referenced to the midgap Fermi level  $E_i$  in the nominally undoped channel:

$$\varphi_{S} = \frac{kT}{q} \cdot \ln\left(\frac{N_{S}}{n_{i}}\right)$$

$$\varphi_{G} = V_{GS} + V_{FB}$$

$$\varphi_{C} = V_{C} + V_{biC}$$

(5)

In Eq. (5),  $n_i$  is the carrier concentration of intrinsic channel material,  $N_S$  is the source doping concentration,  $V_{FB}$  is the flat-band voltage and  $V_{biC}$  is the built-in potential of the inverted channel. Generally, in a bulk device  $V_{biC}$  equals  $2\phi_B$ , where  $\phi_B$  is Fermi potential (difference between the channel Fermi level and midgap  $E_i$  [20]). However, in a lightly doped, fully depleted SOI MOSFETS,  $V_{biC}$  has a more complicated form [24].

We find that the surface potential increases almost exponentially from the channel  $\varphi_{\rm C}$  to source  $\varphi_{\rm S}$ , as illustrated in Fig. 11b. This potential profile determines that the shortest tunneling barrier width  $L_{\rm TW}$  lies along the source-channel direction and is determined by the point where the surface potential falls  $\sim E_{\rm C}/q$  below the source potential  $\varphi_{\rm S}$ . We can now insert the mean electric field in the tunneling direction  $E_{\rm TW}$  along  $L_{\rm TW}$  into Eq. (1), as this has been shown to give better accuracy than the local  $E_{\rm max}$  [11,22]. The analytical expression of the tunneling current becomes:

$$\begin{split} I_{D} &= A_{K} \cdot E_{TW}^{2} \cdot exp\left(-\frac{B_{K}}{E_{TW}}\right) \quad with \ E_{TW} = \frac{E_{G}}{q \cdot L_{TW}} \\ &= \frac{E_{G}}{q} \frac{1}{L_{d} \cdot ln \left[\frac{(\phi_{S} - \phi_{G} + \sqrt{(\phi_{S} - \phi_{G})^{2} - (\phi_{C} - \phi_{G})^{2}}}{\left(\phi_{S} - \phi_{G} - \frac{E_{G}}{q}\right) + \sqrt{\left(\phi_{S} - \phi_{G} - \frac{E_{G}}{q}\right)^{2} - (\phi_{C} - \phi_{G})^{2}}}\right]} \quad and \\ L_{d} &= \sqrt{\frac{\mathcal{E}_{S}}{\mathcal{E}_{ox}} \cdot T_{ox} \cdot T_{s}} \end{split}$$

(6)

where  $L_{\rm d}$  is the characteristic decay length of the potential profile [23]. By substituting the Eq. (4) into Eq. (5) to obtain  $\varphi_{\rm C}$  in the two operating regimes, the tunneling current can be calculated via Eq. (6).

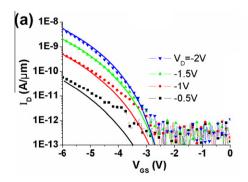

The remaining unknowns are the tunneling parameters  $A_K$  and  $B_{\rm K}$ , which are often estimated for a one-dimensional tunneling junction assuming a constant electric field [13]. Instead, we will treat them as fitting parameters extracted from an experimental  $I_D$ – $V_{GS}$  curve under a fixed  $V_D$  and then used over the entire range of  $V_{GS}$  and  $V_{D}$ . For all of our devices, the extracted  $B_{K}$  value is ~24 MV/cm, which is consistent with other reports [12,22]. Fig. 12 shows a comparison between our model (lines) and the experimental results (dots) of a PTFET with 6 nm SiO2 gate oxide over a wide range of  $V_{CS}$  and  $V_{D}$ . The model reproduces measured  $I_{\rm D}$  reasonably well over most of the biasing range, indicating its validity in both the linear and saturation regimes of the TFET channel. The discrepancy at low  $V_D$  and  $V_{GS}$  in both the  $I_D$ – $V_{GS}$  and  $I_D$ – $V_D$ characteristics may be due to trap-assisted tunneling that is not captured by Eq. (6). A more detailed discussion of our seriesconnected diode and MOSFET model, including its extension to other channel materials and device architectures, will be reported separately [25].

Fig. 12. Quantitative fit between model (lines) and experimental results (dots) of (a)  $I_D$ – $V_{CS}$  and (b)  $I_D$ – $V_D$  curves of SOI TFET with gate oxides of 6 nm SiO<sub>2</sub>.

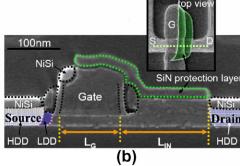

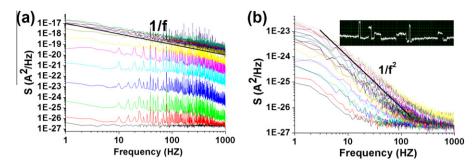

Fig. 13. Comparison of LFN spectra between NMOSFET ( $L_G$  = 350 nm,  $V_{DS}$  = 50 mV,  $V_{GS}$  = 0.1–1.5 V) (a) and NTFET ( $L_G$  = 5  $\mu$ m,  $V_{DS}$  = 1 V,  $V_{GS}$  = 3–5 V) (b). The inset image shows the RTS signal in NTFET.

#### 3.5. Low frequency noise (LFN) characteristics

The LFN caused by the carrier trapping–detrapping process in the slow oxide traps near the channel-dielectric interface has a 1/f signature in MOSFETs. As the area of MOSFET decreases below  $1~\mu\text{m}^2$ , only a few slow oxide traps exist in the entire device, leading to a random telegraph signal (RTS) current noise. The RTS produces a Lorentzian spectrum whose slope is  $1/f^2$  [14].

Fig. 13 compares the LFN of NMOSFET and NTFETs with the same 6 nm SiO<sub>2</sub> gate oxides showing totally different spectral behavior. In the NMOSFET with a gate area of  $3.5 \, \mu m^2$  ( $L_G = 350 \, \text{nm}$ ) the LFN is 1/f, whereas in the NTFET, the spectrum of the noise is Lorentzian with  $1/f^2$  slope even though it is much larger (area =  $25 \, \mu m^2$ ,  $L_G = 5 \, \mu m$ ). The random telegraph signal can also be observed from the inset image in Fig. 13b, in which two or three trapping–detrapping events are visible.

For TFET, the current is mainly determined by the junction tunneling rate, while the channel provides a way for carrier transport to the drain. The trapping of carriers into the oxide above the channel can only cause the fluctuation of the channel conductance, whereas the tunneling rate at the tunneling junction stays stable. The tunneling rate can only be affected by the trapping process at the  $\text{Si/SiO}_2$  interface above the tunneling junction, which is very narrow (around 10 nm). Hence, the effective LFN-generating area of the TFET is very small (0.05  $\mu$ m²), including only a discrete numbers of traps, just as in a very small MOSFET. This is why the RTS noise is observed in TFET even though its gate area is nominally large. Conversely, the measured RTS noise confirms that carrier tunneling acts as the primary mechanism in our TFETs. A more detailed discussion of LFN in TFETs, including device-to-device variability, is available in Ref. [26].

### 4. Conclusions

In this paper, we report on the various aspects of Si TFET performance. We demonstrate that the use of HfO<sub>2</sub> gate oxide with smaller EOT leads to a lower threshold  $V_T$  and subthreshold slope S than identically processed thick SiO<sub>2</sub> oxide TFETs, with S decreasing by a factor of  $\sim$ 3. We show that the introduction of an intrinsic region  $L_{\mathrm{IN}}$  between the channel and the drain in both types of TFETs can largely suppress the  $I_{LEAK}$  without impacting  $I_{ON}$ . The required  $L_{IN}$ falls in the 50-100 nm range, depending on the dopant diffusion. We propose a new TFET model combining the gated tunneling junction in series with the MOSFET channel, which reproduces experimental data over a wide range of drain and gate bias. Finally, we report on low-frequency noise in MOSFET and TFETs and demonstrate that in TFETs the random telegraph signal noise is dominant even in large gate area devices. This is so because the tunneling junction area that determines the current is much smaller than the physical gate length  $L_G$ .

#### Acknowledgments

The work at MINATEC is funded by the RTRA program of the Grenoble Nanosciences Foundation. One of the authors (AZ) also acknowledges support by the US National Science Foundation (award ECCS-0701635).

#### References

- [1] Reddick WM, Amaratunga GAJ. Silicon surface tunnel transistor. Appl Phys Lett 1995;67:494.

- [2] Zhang Q, Seabaugh A. Can the interband tunnel FET outperform Si CMOS? In: Tech Dig DRC; 2008. p. 73–4.

- [3] Khatami Y, Banerjee K. Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE TED 2009;56:2752.

- [4] Leonelli D, Vandooren A, Rooyackers R, Verhulst AS, De Gendt S, Heyns MM, et al. Multiple-gate tunneling field effect transistors with sub-60 mV/dec subthreshold slope. In: Tech Dig SSDM; 2009. p. 767–8.

- [5] Mayer F, Le Royer C, Damlencourt J-F, Romanjek K, Andrieu F, Tabone C, Previtali B, Deleonibus S. Impact of SOI, Si<sub>1-x</sub>Ge<sub>x</sub>OI and GeOI substrates on CMOS compatible tunnel FET performance. In: Tech. Dig. IEDM; 2008. p. 163-6.

- [6] Kazazis D, Jannaty P, Zaslavsky A, Le Royer C, Tabone C, Clavelier L, et al. Tunneling field-effect transistor with epitaxial junction in thin germanium-oninsulator. Appl Phys Lett 2009;94:263508.

- [7] Krishnamohan T, Kim D, Raghunathan S, Saraswat K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and «60 mV/dec subthreshold slope. In: Tech Dig IEDM; 2008. p. 947–9.

- [8] Nayfeh OM, Hoyt JL, Antoniadis D. Strained-Si<sub>1-x</sub>Ge<sub>x</sub>/Si band-to-band tunneling transistors: impact of tunnel-junction Ge composition and doping concentration on switching behavior. IEEE TED 2009;56:2264.

- [9] Kim SH, Kam H, Hu C, Liu TJ-K. Germanium-source tunnel field effect transistors with record high  $I_{\rm ON}$  / $I_{\rm OFF}$ . In: Tech Dig VLSI Symp; 2009. p. 178–9.

- [10] Chen S, Ong S-L, Heng C-H, Samudra G, Yeo Y-C. A variational approach to the two-dimensional nonlinear Poisson's equation for the modeling of tunneling transistors. IEEE EDL 2008;29:1252–5.

- [11] Verhulst AS, Sorée B, Leonelli D, Vandenberghe WG, Groeseneken G. Modeling the single-gate, double-gate, and gate-all-around tunnel field-effect transistor. Appl Phys 2010;107:024518.

- [12] Bardon MG, Neves HP, Puers R, Hoof CV. Pseudo-two-dimensional model for double-gate tunnel FETs considering the junction depletion regions. IEEE TED 2010:57:827.

- [13] Kane EO. Theory of tunneling. J Appl Phys 1961;32:83.

- [14] Akarvardar K, Dufrene BM, Cristoloveanu S, Gentil P, Blalock BJ, Mojarradi MM. Low-frequency noise in SOI four-gate transistors. IEEE TED 2006;53:829–35.

- [15] Ghibaudo G, Boutchacha T. Electrical noise and RTS fluctuations in advanced CMOS devices. Microelectron Reliab 2002;42:573–82.

- [16] Aydin C, Zaslavsky A, Luryi S, Cristoloveanu S, Mariolle D, Fraboulet D, et al. Lateral interband tunneling transistor in silicon-on-insulator. Appl Phys Lett 2004;84:1780.

- [17] Choi WY, Park BG, Lee JD, Liu TK. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE EDL 2007;28:743-5.

- [18] Nagavarapu V, Jhaveri R, Woo JCS. The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE TED 2008;55:1013-9.

- [19] Verhulst AS, Vandenberghe WG, Maex K, Groeseneken G. Tunnel field-effect transistor without gate-drain overlap. Appl Phys Lett 2007;91:05312.

- [20] Sze SM. Physics of semiconductor devices. 2nd ed. New York: Wiley; 1981.

- [21] Dobrovolsky V, Rossokhaty V, Cristoloveanu S. Solid-State Electron 2006;50:754.

- [22] Solomon PM, Jopling J, Frank DJ, D'Emic C, Dokumaci O, Ronsheim P, et al. Universal tunneling behavior in technologically relevant P/N junction diodes. J Appl Phys 2004;95:5800.

- [23] Colinge J. Multi-gate SOI MOSFETs. Solid-State Electron 2004;48:897.

- [24] Mazhari B, Ioannou DE. Surface potential at threshold in thin-film SO1 MOSFET's. IEEE TED 1993;40:1129.

- [25] Wan J, Le Royer C, Zaslavsky A, Cristoloveanu S. A tunneling field effect transistor model combining interband tunneling with channel transport. J Appl Phys 2011, submitted for publication.

- [26] Wan J. Le Royer C. Zaslavsky A, Cristoloveanu S. Low-frequency noise behavior of tunneling field effect transistors. Appl Phys Lett 2010;97:243503.