## Strong room-temperature negative transconductance in an axial Si/Ge hetero-nanowire tunneling field-effect transistor

Peng Zhang, <sup>1</sup> Son T. Le, <sup>2</sup> Xiaoxiao Hou, <sup>1</sup> A. Zaslavsky, <sup>1</sup> Daniel E. Perea, <sup>3</sup> Shadi A. Dayeh, <sup>4,5</sup> and S. T. Picraux <sup>4</sup>

<sup>1</sup>Department of Physics and School of Engineering, Brown University, Providence, Rhode Island 02912, USA <sup>2</sup>Semiconductor and Dimensional Metrology Division, National Institute of Standards and Technology, Gaithersburg, Maryland 20899, USA

<sup>3</sup>Environmental and Molecular Sciences Laboratory, Pacific Northwest National Laboratory, Richland, Washington 99352, USA

<sup>4</sup>Center for Integrated Nanotechnologies, Los Alamos National Laboratory, Los Alamos, New Mexico 87545, USA

<sup>5</sup>Department of Electrical and Computer Engineering, University of California, San Diego, California 92093, USA

(Received 16 June 2014; accepted 1 August 2014; published online 12 August 2014)

We report on room-temperature negative transconductance (NTC) in axial Si/Ge hetero-nanowire tunneling field-effect transistors. The NTC produces a current peak-to-valley ratio >45, a high value for a Si-based device. We characterize the NTC over a range of gate  $V_{\rm G}$  and drain  $V_{\rm D}$  voltages, finding that NTC persists down to  $V_{\rm D} = -50\,\rm mV$ . The physical mechanism responsible for the NTC is the  $V_{\rm G}$ -induced depletion in the p-Ge section that eventually reduces the maximum electric field that triggers the tunneling  $I_{\rm D}$ , as confirmed via three-dimensional (3D) technology computer-aided design simulations. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4892950]

Since the pioneering work of Esaki on the negative differential resistance (NDR) in highly doped p-n junctions due to interband tunneling of carriers through a narrow potential barrier, NDR and negative transconductance (NTC) devices based on quantum mechanical tunneling have been heavily investigated because of their potential applications in lowpower inverter logic, memory, and high-speed switching circuits.<sup>2–7</sup> However, most of the early results were based on III-V semiconductors and suffered from the relatively low peak-to-valley ratio (PVR) at room temperature. Since then, many efforts were made to improve the device performance in silicon technology-compatible materials, including Si<sup>8</sup> and Si/SiGe<sup>9</sup> diodes based on forward-biased interband tunneling with improved PVR (~5), Si-based field-effect transistors, <sup>10–12</sup> as well as new materials such as Ge-on-insulator, 13,14 and Ge<sub>x</sub>C<sub>1-x</sub> metal-oxide-semiconductor fieldeffect transistors. 15 Recently, semiconductor nanowires (NWs) have received much attention, and room-temperature NDR was reported in InP,<sup>16</sup> Si,<sup>17</sup> and Si/SiGe<sup>18</sup> NWs. Silicon-based NTC devices operating at room temperature with high PVR would have the added advantage of plausible compatibility with modern silicon technology.

Here, we report on NTC in an axial Si/Ge hetero-NW tunneling field-effect transistor (TFET) structure with PVR >45, a high value for room-temperature operation in any material, but especially in Si. The NTC persists over a large range of drain voltage  $|V_{\rm D}|$  down to 50 mV and a reasonably low gate voltage  $|V_{\rm G}| < 1.5$  V. The NTC is repeatable, reproducible from device to device, and is observed in both up and down  $V_{\rm G}$  sweep directions, with some hysteresis due to charge trapping at the insulator/semiconductor interface, as verified by technology computer-aided design (TCAD) simulations.

The axial *n*-Si/*i*-Si/*p*-Ge hetero-NWs were grown on Ge (111) substrate by an Au-catalyzed vapor-liquid-solid (VLS) chemical vapor deposition method, <sup>19,20</sup> The growth details

can be found in a previous publication. <sup>21</sup> The *p-i-n* NW segments were  $\sim 2.5 \, \mu m$  *p*-Ge,  $\sim 1.6 \, \mu m$  *i*-Si, and  $\sim 3.4 \, \mu m$  *n*-Si, with a diameter of  $\sim 55 \, \text{nm}$ . The heterojunction transition between the Ge and Si section is estimated to be  $\sim 20-50 \, \text{nm}$  wide, comparable to the NW diameter. <sup>22</sup> This relatively sharp interfacial transition from 100% Ge to 100% Si for axial NW growth was achieved by *in-situ* switching the VLS liquid growth catalyst from Au to AuGa at the start of Si NW growth. <sup>22</sup> A large fraction of the hetero-NWs are kinked at the Ge/Si junction, which could be avoided by optimizing the growth conditions, <sup>20,22</sup> but they were in fact preferentially chosen during the device fabrication process to help locate the junction for top-gate placement.

After the growth, the NWs were ultrasonically dispersed in isopropanol and spread on a heavily p-doped silicon substrate covered with  $\sim 100 \, \text{nm}$  of thermally grown SiO<sub>2</sub>. Contacts to p-Ge and n-Si, doped in the low to mid-10<sup>18</sup> cm<sup>-3</sup> range, were realized by e-beam lithography (EBL), followed by e-beam evaporation of 120 nm Ni contact metal and lift-off. Thereafter,  $\sim 10 \,\mathrm{nm}$  of high- $\kappa$  HfO<sub>2</sub> was deposited at 200 °C by atomic layer deposition, simultaneously annealing the Ohmic contacts. The top gate electrode was fabricated by a second EBL step, 100 nm Ni evaporation and lift-off. The gate was aligned to cover the intrinsic Si section and parts of the *n*-Si and *p*-Ge sections, as shown in the scanning electron microscope (SEM) image of the final top-gated device in Fig. 1(a). Note that compared to the previously reported TFETs fabricated from hetero-NWs grown in the same batch,<sup>21</sup> here the overlap of the p-Ge section is larger, which, as discussed below, enables the high PVR of our NTC devices.

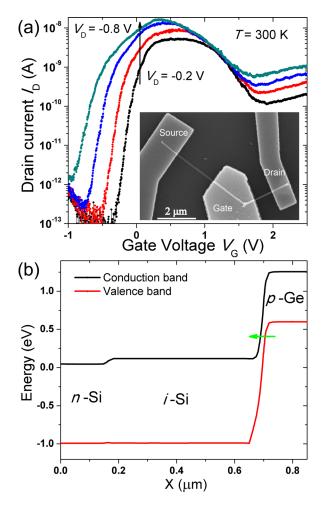

Figure 1(a) shows the  $I_{\rm D}-V_{\rm G}$  transfer characteristics at a fixed reverse source-drain voltage  $V_{\rm D}=-0.2$  to -0.8 V in 0.2 V steps (with *n*-Si source grounded), including the relatively sharp turn-on of the current at a threshold  $V_{\rm T}$  (with the

FIG. 1. (a) Room-temperature  $I_{\rm D}-V_{\rm G}$  transfer characteristics at  $V_{\rm D}=-0.2$  to -0.8 V in 0.2 V steps; inset shows the SEM image of the kinked Si-Ge hetero-NW after the top gate metal deposition. Note that the gate leakage current  $I_{\rm G}<5$  pA for all  $V_{\rm G}$ . (b) TCAD simulation of the conduction and valence band diagram cut along the device length at  $V_{\rm D}=-0.6$  V and  $V_{\rm G}=0.5$  V (the gate overlaps the *i*-Si region, as well as parts of *n*-Si source and *p*-Ge drain).

best subthreshold slope of  $\sim 55 \, \mathrm{mV/decade}$  over  $\sim 3$  orders of  $I_{\mathrm{D}}$  at  $V_{\mathrm{D}} = -0.2 \, \mathrm{V}$ ) followed by current peak at a  $V_{\mathrm{P}}$  in the 0  $< V_{\mathrm{G}} < 1 \, \mathrm{V}$  range, and a strong NTC for  $V_{\mathrm{G}} > V_{\mathrm{P}}$ . Both  $V_{\mathrm{T}}$  and  $V_{\mathrm{P}}$  depend on  $V_{\mathrm{D}}$ , shifting to lower  $V_{\mathrm{G}}$  as  $V_{\mathrm{D}}$  becomes more negative. Figure 1(b) shows the simulated band diagram<sup>23</sup> of the device at the center of the channel along the NW axis in the TFET mode, with reverse-bias  $V_{\mathrm{D}} = -0.6 \, \mathrm{V}$  and  $V_{\mathrm{G}} = 0.5 \, \mathrm{V}$ , where the *i*-Si channel under the gate is flooded with electrons. The arrow indicates electron tunneling controlled by the maximum electric field  $E_{\mathrm{MAX}}$  that, for these bias values, occurs in the narrow-gap Ge drain.

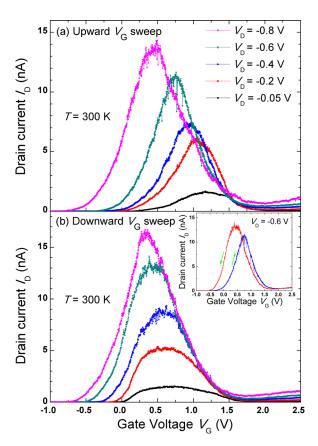

The  $I_{\rm D}-V_{\rm G}$  characteristics of our devices on a linear scale, with a constant reverse  $V_{\rm D}$  applied to the p-Ge contact while keeping n-Si source and Si substrate grounded and sweeping the top-gate voltage  $V_{\rm G}$  are shown in Fig. 2 (several devices were measured and showed similar behavior). Excellent NTC was observed for different  $V_{\rm D}$  with PVR ranging from 20 to >45, with the highest PVR of 47.9 observed at  $V_{\rm D}=-0.2\,\rm V$ . The peak current positions  $V_{\rm P}$  and magnitudes vary somewhat depending on whether  $V_{\rm G}$  is swept up from  $V_{\rm G}=-1\,\rm V$  (below threshold voltage  $V_{\rm T}$ ) as in Fig. 2(a), or down from  $V_{\rm G}=2.5\,\rm V$  as in Fig. 2(b). The inset in Fig. 2(b) presents the hysteresis between the upward and

FIG. 2. Measured current-voltage characteristics of the device at different reverse-bias  $V_{\rm D}$  values at room temperature: (a)  $V_{\rm G}$  swept up from  $-1.0\,{\rm V}$  to  $2.5\,{\rm V}$ ; (b)  $V_{\rm G}$  swept down from  $2.5\,{\rm V}$  to  $-1.0\,{\rm V}$ ; inset shows the PVR hysteresis at  $V_{\rm D} = -0.6\,{\rm V}$ . High PVR is observed for both  $V_{\rm G}$  sweep directions.

downward  $V_{\rm G}$  sweeps at  $V_{\rm D}\!=\!-0.6\,\rm V$ . The magnitude of the hysteresis ranges from  $\sim\!0.2\,\rm V$  at  $V_{\rm D}\!=\!-0.8\,\rm V$  to  $\sim\!0.5\,\rm V$  at  $V_{\rm D}\!=\!-0.2\,\rm V$ . We attribute the hysteresis behavior to the charge trapping and detrapping at the Si/HfO<sub>2</sub> and Ge/HfO<sub>2</sub> interfaces, consistent with the TCAD simulations discussed below. It is likely that the hysteresis could be reduced by post-deposition annealing at elevated temperature in N<sub>2</sub> ambient; <sup>24,25</sup> conversely such charge-trapping-induced hysteresis may have memory applications.

Turning to the physical mechanism responsible for the NTC, we emphasize that, unlike some reported NTC devices where the decrease in  $I_D$  was due to current diverted to gate leakage,  $I_G$ , in our device  $I_G < 5$  pA for all  $V_G$ . Therefore, the NTC behavior should be explained by the tunneling at the heterojunction. The physical mechanism responsible for the NTC behavior is as follows: in the  $V_{\rm T} < V_{\rm G} < V_{\rm P}$  gate bias range, tunneling current increases as a result of the decreasing of the tunnel-barrier width. However, when  $V_{\rm G}$ exceeds  $V_{\rm P}$ , tunneling current drops because the gate voltage begins to deplete carriers in the p-Ge section resulting in lower  $E_{\rm MAX}$  at the tunneling heterojunction. Note that a weak NTC signature was observed in our previous hetero-NW TFET publication,<sup>21</sup> but the effect is stronger when the overlap of the top gate over the p-Ge section is larger, as in our case here, which further supports the postulated NTC mechanism.

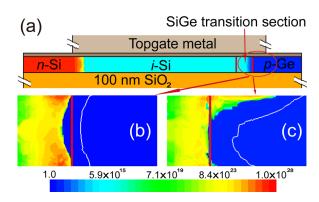

In order to verify our experimental result, 3D TCAD simulations were performed using Synopsys Sentaurus.<sup>23</sup> A two-dimensional cross-section through the middle of the

device along the hetero-NW is shown in Fig. 3(a). The simulation set-up is similar to that described in Ref. 21, except that the overlap over the p-Ge section of the top gate contact is 20 nm longer, which will effectively deplete carriers in p-Ge section near the junction at high  $V_{\rm G}$ . The doping of the p-Ge and n-Si was taken as  $5\times 10^{18}\,{\rm cm}^{-3}$ . The decay of the doping into i-Si (assumed to be  $10^{15}\,{\rm cm}^{-3}$  p-Si due to background doping) was taken as 6 nm per decade of doping and the SiGe transition section was assumed to occur linearly over 50 nm. <sup>22</sup> Since the Ge/high- $\kappa$  surface is known to have a high trap density,<sup>27</sup> which is a main cause of the threshold voltage instability,<sup>28</sup> a positive interface charge density  $N_{\rm T} \sim 10^{13}\,{\rm cm}^{-2}$  was assumed to shift the threshold voltage  $V_{\rm T}$  to approximately our experimental value. Figures 3(b) and 3(c) show, respectively, the spatial distribution of electron band-to-band tunneling generation at the tunneling junction at  $V_D = -0.6 \,\mathrm{V}$  with  $V_G = 0 \,\mathrm{V}$  (below  $V_P$ ) and  $V_G = 1 \,\mathrm{V}$ (above  $V_P$ , in the NTC part of the characteristic, see Fig. 1(a)). As evident from the figure, electrons tunnel from valence band of the p-Ge drain to the conduction band of the i-Si channel and the predicted tunneling generation at  $V_G = 0 \text{ V}$  (Fig. 3(b)) is larger than that of at  $V_G = 1 \text{ V}$ (Fig. 3(c)). The edges of the depletion region, shown by the white line in both figures, indicate how the highly doped drain has been depleted by the electric field due to the higher gate bias at  $V_G = 1$  V, resulting in lower  $E_{MAX}$  at the tunneling heterojunction and thus decreasing  $I_D$ .

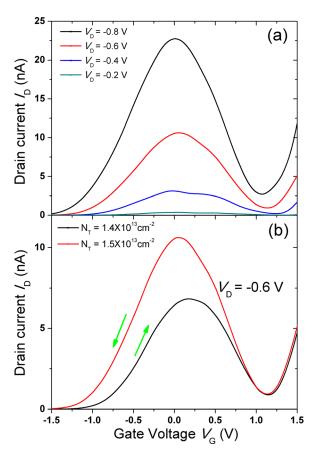

The resulting simulated  $I_{\rm D}-V_{\rm G}$  curves at constant  $V_{\rm D}$  are shown in Fig. 4. As can be seen, the simulation results in Fig. 4(a) are in reasonable quantitative agreement with the measured results in Fig. 2, including a simulated current PVR in the 10–30 range. Reproducing the hysteresis in the NTC with respect to the  $V_{\rm G}$  sweep direction, a slightly higher  $N_{\rm T}=1.5\times10^{13}\,{\rm cm}^{-2}$  was assumed for the downward  $V_{\rm G}$  sweep than the  $N_{\rm T}=1.4\times10^{13}\,{\rm cm}^{-2}$  for the upward sweep, consistent with the additional charging of the interface by the high  $I_{\rm D}$  flowing through the TFET at  $V_{\rm G}=2.5\,{\rm V.}^{29}$  As shown in Fig. 4(b), the location of peak current shifted

FIG. 3. (a) A cross-section through the hetero-NW in the 3D Sentaurus TCAD model: an *n*-doped Si substrate (not shown), a 100 nm thick SiO<sub>2</sub>, a straight cylindrical NW of 50 nm diameter, a 10 nm thick HfO<sub>2</sub> gate oxide, and nickel "omega" gate metal (not to scale). Vertical lines in the channel indicate the boundaries of the SiGe transition region between *i*-Si channel and *p*-Ge drain; (b) and (c) Spatial distribution of band-to-band tunneling generation at the drain side at  $V_{\rm D}\!=\!-0.6\,{\rm V}$  with (b)  $V_{\rm G}\!=\!0$  and (c)  $V_{\rm G}\!=\!1\,{\rm V}$ . The white line in (b) and (c) indicates the edge of the depletion region in the *p*-Ge drain. The color scale bar indicates the magnitude of the generation in cm<sup>-3</sup>·s<sup>-1</sup>. Note the higher predicted tunneling generation (red-colored regions) at  $V_{\rm G}\!=\!0$  (b) than at  $V_{\rm G}\!=\!1\,{\rm V}$  (c).

FIG. 4. (a) Simulated  $I_D-V_G$  characteristics at constant  $V_D$  in 0.2 V step at  $T=300\,\mathrm{K}$ ; (b) Simulated  $I_D-V_G$  characteristics with a slightly higher  $N_T=1.5\times10^{13}\,\mathrm{cm}^{-2}$  for the downward  $V_G$  sweep than the  $N_T=1.4\times10^{13}\,\mathrm{cm}^{-2}$  for the upward sweep, reproducing both the hysteresis and the peak current position and magnitude observed in measured data.

negatively and the current increases at higher  $N_{\rm T}$ , in agreement with our experimental data in Fig. 2.

In summary, we have demonstrated strong room-temperature NTC in axial n-Si/i-Si/p-Ge hetero-NW TFETs with HfO $_2$  gate dielectric. The highest PVR of 47.9 was observed at reverse bias voltage of -0.2 V. We explain it by the  $V_G$ -induced depletion in the p-Ge section that eventually reduces the maximum electric field, which was confirmed by a 3D Sentaurus TCAD simulation. The ability to achieve a high PVR in Si-based devices at room temperature may be a step towards the realization of its application in logic and memory circuits.

The work at Brown was supported by the NSF (awards ECCS-1068895 and DMR-1203186). Hetero-nanowire epitaxy was performed at the Center for Integrated Nanotechnologies, a U.S. Department of Energy, Office of Basic Energy Sciences user facility at Los Alamos National Laboratories (Contact No. DE-AC52-06NA25396) and Sandia National Laboratories (Contract No. DE-AC04-94AL85000). We also acknowledge user support from EMSL, a DOE Office of Science User Facility sponsored by the Office of Biological and Environmental Research and located at Pacific Northwest National Laboratory.

<sup>&</sup>lt;sup>1</sup>L. Esaki, Phys. Rev. **109**, 603 (1958).

<sup>&</sup>lt;sup>2</sup>S. Luryi and F. Capasso, Appl. Phys. Lett. 47, 1347 (1985).

<sup>&</sup>lt;sup>3</sup>F. Capasso, S. Sen, and A. Y. Cho, Appl. Phys. Lett. **51**, 526 (1987).

- <sup>4</sup>F. Beltram, F. Capasso, S. Luryi, S.-N. G. Chu, A. Y. Cho, and D. L. Sivco, Appl. Phys. Lett. **53**, 219 (1988).

- <sup>5</sup>A. Zaslavsky, D. C. Tsui, M. Santos, and M. Shayegan, Appl. Phys. Lett. 58, 1440 (1991).

- <sup>6</sup>ç, Kurdak, D. C. Tsui, S. Parihar, M. B. Santos, H. C. Manoharan, S. A. Lyon, and M. Shayegan, Appl. Phys. Lett. 64, 610 (1994).

- <sup>7</sup>T. Uemura and T. Baba, IEEE Electron Device Lett. **18**, 225–227 (1997).

- <sup>8</sup>M. Oehme, D. Hähnel, J. Werner, M. Kaschel, O. Kirfel, E. Kasper, and J. Schulze, Appl. Phys. Lett. 95, 242109 (2009).

- <sup>9</sup>A. Ramesh, P. R. Berger, and R. Loo, Appl. Phys. Lett. **100**, 092104 (2012).

- <sup>10</sup>R. Versari and B. Riccò, IEEE Trans. Electron Devices **46**, 1189 (1999).

- <sup>11</sup>K. R. Kim, D. H. Kim, S.-K. Sung, J. D. Lee, and B.-G. Park, IEEE Electron Device Lett. 23, 612 (2002).

- <sup>12</sup>K. R. Kim, H. H. Kim, Ki-Whan Song, J. I. Huh, J. D. Lee, and B.-G. Park, IEEE Trans. Nanotechnol. 4, 317 (2005).

- <sup>13</sup>A. Zaslavsky, S. Soliveres, C. L. Royer, S. Cristoloveanu, L. Clavelier, and S. Deleonibus, Appl. Phys. Lett. **91**, 183511 (2007).

- <sup>14</sup>D. Kazazis, A. Zaslavsky, E. Tutuc, N. A. Bojarczuk, and S. Guha, Semicond. Sci. Technol. 22, S1 (2007).

- <sup>15</sup>En-Shao Liu, D. Q. Kelly, J. P. Donnelly, E. Tutuc, and S. K. Banerjee, IEEE Electron Device Lett. 30, 136 (2009).

- <sup>16</sup>J. Wallentin, P. Wickert, M. Ek, A. Gustafsson, L. R. Wallenberg, M. H. Magnusson, L. Samuelson, K. Deppert, and M. T. Borgström, Appl. Phys. Lett. 99, 253105 (2011).

- <sup>17</sup>H. Schmid, C. Bessire, M. T. Björk, A. Schenk, and H. Riel, Nano Lett. 12, 699 (2012).

- <sup>18</sup>W. Y. Fung, L. Chen, and W. Lu, Appl. Phys. Lett. **99**, 092108 (2011).

- <sup>19</sup>S. A. Dayeh and S. T. Picraux, ECS Trans. **33**, 373 (2010).

- <sup>20</sup>S. A. Dayeh, J. Wang, N. Li, J. Y. Huang, A. V. Gin, and S. T. Picraux, Nano Lett. 11, 4200 (2011).

- <sup>21</sup>S. T. Le, P. Jannaty, Xu Luo, A. Zaslavsky, D. E. Perea, S. A. Dayeh, and S. T. Picraux, Nano Lett. **12**, 5850 (2012).

- <sup>22</sup>D. E. Perea, N. Li, R. M. Dickerson, A. Misra, and S. T. Picraux, Nano Lett. 11, 3117 (2011).

- <sup>23</sup>Synopsis Sentaurus TCAD ver. H-2013.03 using nonlocal band-to-band tunneling model.

- <sup>24</sup>L. Kang, B. H. Lee, W.-J. Qi, Y. Jeon, R. Nieh, S. Gopalan, K. Onishi, and J. C. Lee, IEEE Electron Device Lett. 21, 181 (2000).

- <sup>25</sup>M. Cho, H. B. Park, J. Park, C. S. Hwang, J.-C. Lee, Se-Jung Oh, J. Jeong, K. S. Hyun, H.-S. Kang, Y.-W. Kim, and J.-H. Lee, J. Appl. Phys. 94, 2563 (2003).

- <sup>26</sup>B. C. Lai and J. Y. Lee, IEEE Electron Device Lett. **22**, 142 (2001).

- <sup>27</sup>A. Dimoulas and P. Tsipas, Microelectron. Eng. **86**, 1577 (2009).

- <sup>28</sup>S. Zafar, A. Kumar, E. Gusev, and E. Cartier, IEEE Trans. Device Mater. Reliab. 5, 45 (2005).

- <sup>29</sup>C. Thelander, L. E. Fröberg, C. Rehnstedt, L. Samuelson, and Lars-Erik Wernersson, IEEE Electron Device Lett. 29, 206 (2008).