Received 5 April 2019; accepted 17 May 2019. Date of publication 22 May 2019; date of current version 23 August 2019.

The review of this paper was arranged by Editor N. Sugii.

Digital Object Identifier 10.1109/JEDS.2019.2918203

# Dynamic Coupling Effect in Z<sup>2</sup>-FET and Its Application for Photodetection

J. LIU<sup>10</sup> 1, X. Y. CAO<sup>10</sup> 1, B. R. LU<sup>10</sup> 1, Y. F. CHEN<sup>1</sup>, A. ZASLAVSKY<sup>2</sup>, S. CRISTOLOVEANU<sup>10</sup> 3, AND J. WAN<sup>1</sup>

1 State Key Laboratory of ASIC and System, School of Information Science and Engineering, Fudan University, Shanghai 200433, China 2 Department of Physics and School of Engineering, Brown University, Providence, RI 02912, USA 3 IMEP-LAHC, INP-Grenoble/Minatec, 38016 Grenoble, France

CORRESPONDING AUTHOR: J. WAN (e-mail: jingwan@fudan.edu.cn)

The work of J. Liu, X. Y. Cao, B. R. Lu, Y. F. Chen, and J. Wan was supported by the Natural Science Foundation of Shanghai under Grant 17ZR1446700.

**ABSTRACT** In this paper, the application of the zero subthreshold swing and zero impact ionization FET ( $Z^2$ -FET) for photodetection is studied with TCAD simulation. Dynamic coupling effect is utilized to form carrier injection barriers in the partially depleted silicon-on-insulator (PD-SOI) film. Photoelectron accumulation at the front gate interface lowers the hole injection barrier and modulates the turn-on voltage. The light-triggering threshold of the device can be tuned by the front gate voltage, which controls the injection barrier height. We explore two operation modes suited to different applications, and demonstrate the operation of a one-transistor active pixel sensor array. Unlike other image sensors that utilize only one type of carrier, the  $Z^2$ -FET photodetector uses photo-generated holes to induce high electron currents through internal amplification, leading to a high sensitivity of up to  $1.8 \times 10^5$  e-/(lux·s).

**INDEX TERMS** Z<sup>2</sup>-FET, dynamic coupling effect, silicon-on-insulator, photodetection.

#### I. INTRODUCTION

The ultra-thin body and buried oxide (UTBB) silicon-oninsulator (SOI) technology is extensively used in advanced integrated circuits (ICs) due to its remarkable advantages [1]-[4]. Devices on SOI substrates obtain performance gains via reduced parasitic capacitance and leakage current, as well as threshold voltage tuning [5], [6]. Thus, the SOI platform is of great interest in many application fields, such as SOI-based electron-photonic integrated circuits (EPICs) and next-generation systems-on-chip with low power consumption and high speed [7]-[9]. Besides, thanks to their high tolerance to transient radiation effects, SOI substrates are also favored in aerospace applications [10]. Other applications, such as optical communication, image sensing, and photodetection are also widely explored in SOI because of high radiation hardness, as well as compatibility with SOI electronics and photonics [11]–[14]. Thus, photodetectors based on various operation mechanisms, using diodes, transistors and interface coupling effects (ICPDs) have been demonstrated in SOI technology [15]-[18].

Developed in fully depleted SOI (FD-SOI), the  $Z^2$ -FET naturally retains many of the above-described advantages

of SOI-based devices. The  $Z^2$ -FET is a forward-biased p-i-n diode partially covered with a top gate. Based on the band-modulation operation mechanism, it shows pronounced sharp-switching characteristics [19], [20]. Essentially, the band modulation in  $Z^2$ -FET triggers a positive feedback between the flow of carriers and their injection barriers, achieving outstanding electrical performance with low subthreshold swing and high  $I_{ON}/I_{OFF}$  ratio [21]. Besides, the  $Z^2$ -FET exhibits gate-controlled hysteresis in its output characteristics. Thanks to these unusual properties, the  $Z^2$ -FET has shown promise in a series of applications, such as electrostatic discharge (ESD) protection [22], [23], dynamic random access memory (DRAM) [24], [25], and novel flash memory [26].

In this work, we extend the application of the  $Z^2$ -FET to photodetection, systematically studied with TCAD simulation in Synopsys Sentaurus. Instead of using an FD-SOI substrate, partially-depleted SOI (PD-SOI) with a thicker  $T_{Si}$  top Si layer is exploited to improve light absorption. The dynamic coupling effect [27] is investigated and utilized in the  $Z^2$ -FET to rebuild carrier injection barriers. Under illumination, photogenerated electrons accumulate under the top

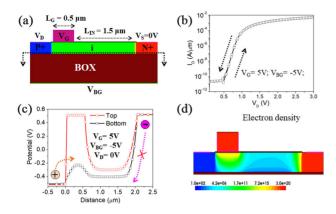

FIGURE 1. (a) Schematic view of the simulated Z²-FET with  $L_G=0.5~\mu m$ ,  $L_{IN}=1.5~\mu m$ , 200 nm top silicon film  $(T_{Si})$  and 500 nm buried oxide  $(T_{BOX})$ . (b) Simulated output characteristics with forward and backward sweeps under  $V_G=5$  V and  $V_{BG}=-5$  V. (c) Potential barriers along the channel direction near the top and bottom interfaces. (d) Electron density distribution in the device, showing electron inversion under the front gate.

gate and screen the coupling. This lowers the carrier injection barrier and eventually triggers the positive feedback that turns on the device. We explore different operation modes suited to multiple potential applications and study the impact of photo-generated hole density and  $T_{\rm Si}$  on sensitivity. Finally, we simulate one-transistor active pixel sensor (APS) array operation and benchmark our device against other reported CMOS-based photodetectors.

## II. DYNAMIC COUPLING EFFECT IN PD-SOI Z<sup>2</sup>-FET

#### A. DEVICE STRUCTURE AND OPERATING PRINCIPLE

The conventional  $Z^2$ -FET is built on the FD-SOI platform with an ultrathin top Si layer  $(T_{Si})$ . The front and back gate biasing effectively creates hole and electron injection barriers next to the drain and source electrode respectively. However, an FD-SOI substrate with ultra-thin  $T_{Si}$  suffers from poor light absorption efficiency. The absorption depth in Si is larger than 200 nm in the visible and increases with wavelength  $\lambda$  [28], so  $T_{Si}$  needs to be relatively large for effective photodetection purpose. At the same time, a thicker  $T_{Si}$  will reduce front-gate  $V_G$  control of the bottom interface, thereby degrading the turn-on voltage  $V_{ON}$ . As a result, our simulations use a compromise value  $T_{Si}=200$  nm for illumination at  $\lambda=500$  nm. A systematic study of  $T_{Si}$  in our  $Z^2$ -FET photodetector is presented in Section VI.

Figure 1(a) shows the partially-depleted  $Z^2$ -FET structure we use in our simulations, with  $T_{Si}=200$  nm as in [15], [18] and a p-type doping concentration of  $10^{15}$  cm<sup>-3</sup>. The front gate length is  $L_G=0.5~\mu m$  and intrinsic length (region not covered by front gate) is  $L_{IN}=1.5~\mu m$ . The thicknesses of BOX and front-gate oxide are 500 and 10 nm respectively (making it possible to apply  $V_G$  up to 9 V without gate leakage). Our simulations use electric field and doping-dependent mobility, and SRH thermal generation-recombination with a doping-dependent carrier lifetime of 0.1  $\mu$ s. A direct current (DC) simulation of the output characteristics by sweeping  $V_D$  from 0 to 3 V and then back, at

fixed  $V_G = 5$  V and  $V_{BG} = -5$  V is shown in Fig. 1(b). In contrast to the FD-SOI based Z<sup>2</sup>-FET with ultrathin T<sub>Si</sub>, the output characteristics of the device based on PD-SOI substrate show neither sharp switching nor gate-controlled hysteresis. This can be understood by investigating the potential profiles along the channel direction extracted at 1 nm below the gate oxide/channel interface (top interface) and 1 nm above channel/BOX interface (bottom interface), shown in Fig. 1(c). The electron injection barriers due to negative V<sub>BG</sub> are high at both top and bottom interfaces. In contrast, the hole injection barrier created by V<sub>G</sub> is high only at top interface, but not at the bottom interface. This is due to the screening of the V<sub>G</sub> > 0 electric field by inversion electron charge accumulating at the top interface, as shown in Fig. 1(d). As a result, the top gate exerts little control over the bottom interface of the channel compared to  $V_{BG} < 0$ , leading to a very low hole injection barrier and eliminating the feedback process and the sharp switching characteristics.

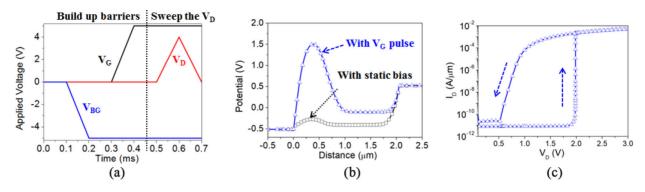

To rebuild the hole injection barrier and recover sharp switching characteristics, we use the dynamic coupling effect triggered by voltage pulse applied on the front gate. In Fig. 2(a), a V<sub>G</sub> pulse rising from 0 to 5 V in 0.1 ms is applied 0.1 ms after the  $V_{BG}$  is pulsed to -5 V. Under a fast V<sub>G</sub> pulse, thermal generation is too slow to produce enough electrons at the top interface and screen the electric field. This non-equilibrium condition results in deep depletion in T<sub>Si</sub>, which rebuilds the hole injection barrier, as shown in Fig. 2(b). This is essentially the same dynamic coupling effect used in SOI-based MOSFETs for DRAM applications [27]. With the rebuilt hole injection barrier, a forward and backward sweep of V<sub>D</sub> from 0 to 3 V, shortly after the V<sub>G</sub> pulse, shows output characteristics with sharp switching and hysteresis, similar to that of a conventional  $Z^2$ -FET, see Fig. 2(c).

# B. IMPACT OF BIAS PULSE SEQUENCE ON INJECTION BARRIERS

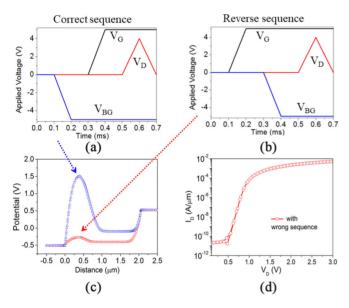

The sequence of the  $V_G$  and  $V_{BG}$  pulses plays a key role in rebuilding the carrier injection barriers, as illustrated in Fig. 3. An unexpected result is observed when order between  $V_G$  and  $V_{BG}$  pulses is swapped, see Fig. 3(b). In this case,  $V_G$  is first pulsed up to 5 V, followed by a  $V_{BG}$  pulse down to -5 V 0.1 ms later (reversing the sequence of Fig. 2(a)). As shown in Fig. 3(c) this reversed sequence fails to rebuild the potential barrier, see the red curve in Fig. 3(c), and suppresses the sharp switching and hysteresis, as shown in Fig. 3(d).

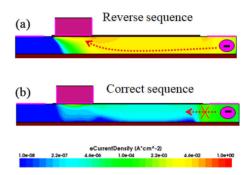

This can be understood by investigating the electron current density distribution inside the device. In the reversed bias sequence, the earlier positive  $V_G$  pulse draws electrons from the  $N^+$ -doped source into the channel. These electrons flow to the front gate interface, as shown in Fig. 4(a). As a result, the accumulated electrons reach equilibrium (steady-state) condition, screen the control from the top gate on the bottom interface, and eliminate the sharp switching. With the correct sequence, the  $V_{BG} < 0$  pulse is applied

FIGURE 2. (a) Bias waveforms applied to the device. (b) Comparison of potential distributions of the device under static and pulsed front-gate biasing. (c) Simulated I<sub>D</sub>-V<sub>D</sub> characteristics of the device under pulsed V<sub>G</sub> operation.

FIGURE 3. (a) Correct and (b) reversed pulsed sequences for dynamic coupling effect in PD-SOI Z<sup>2</sup>-FET. (c) Comparison of potential profiles from two different bias sequences. (d) I<sub>D</sub>-V<sub>D</sub> characteristics of the reversed sequence, showing no sharp switching.

first, preventing electron injection into the intrinsic region, so that the  $V_G>0$  pulse cannot attract electrons from the doped source, as shown in Fig. 4(b). Without electrons at the front interface,  $V_G$  builds up the barrier at the bottom of the film successfully.

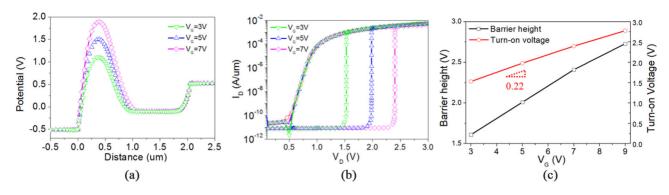

#### C. IMPACT OF $V_G$ MAGNITUDE ON INJECTION BARRIERS

Besides the bias pulse sequence, the front gate voltage can also impact the barrier height and thus modulate the turn-on voltage  $(V_{ON})$  of the device. In a conventional FD-SOI  $Z^2$ -FET,  $V_{ON}$  is linearly controlled by front gate voltage  $V_G$ . The PD-SOI  $Z^2$ -FET based on dynamic coupling exhibits a similar dependence on  $V_G$  magnitude. Figure 5(a) compares potential profiles along the bottom interface for three different  $V_G$  pulses of 3, 5, and 7 V respectively. With higher  $V_G$  pulses, the hole barrier gets taller. As a result, the turn-on voltage  $V_{ON}$  also increases, see Fig. 5(b). Figure 5(c) summarizes the impact of  $V_G$  on hole injection barrier height

FIGURE 4. Electron current density and flow during the ramp of V<sub>G</sub> when the device is biased with (a) reversed and (b) correct pulse sequences of

and  $V_{ON}$ . As  $V_G$  magnitude increases from 3 to 9 V, the hole potential barrier increases linearly from 1.6 to 2.7 V and the  $V_{ON}$  increases linearly from 1.5 to 2.8 V. The modulation ratio R between  $V_{ON}$  and  $V_G$  is 0.22. The gate-controlled sharp-switching characteristic of the PD-SOI  $Z^2$ -FET is helpful for photo- detection. It can directly convert the exposure to a well-defined  $V_{ON}$  without additional amplification. Further, the high internal gain responsible for sharp switching also leads to the high sensitivity of the  $Z^2$ -FET photodetector, as discussed in detail in Sections V and VIII of this paper.

## III. APPLICATION OF Z<sup>2</sup>-FET IN PHOTODETECTION

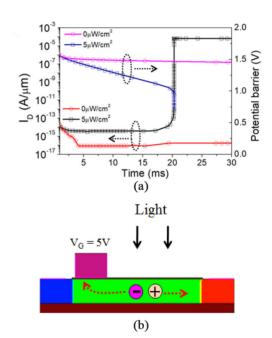

The dynamic coupling effect that forms the hole injection barrier can interact with photo-generated carriers, and thus be used for photodetection. Figure 6 shows the impact of light on our PD-SOI  $Z^2$ -FET. In our simulation, a ray tracing model is used for the optical part of the simulation using conventional boundary conditions. The optical generation is based on a quantum yield with step function model and default complex refractive index of Si is used in the Synopsys Sentaurus. The device is first biased with  $V_{BG}$  and  $V_{G}$  pulses to form the carrier injection barriers. Shortly thereafter, the device is exposed to light pulses of various intensities at the fixed  $\lambda = 500$  nm wavelength, see Fig. 6(a).

The evolution of  $I_D$  is recorded after illumination, as shown in Fig. 6(b). In the dark, the device remains in the

FIGURE 5. (a) Potential profile at the bottom channel vs. V<sub>G</sub>; (b) I<sub>D</sub>-V<sub>D</sub> characteristics at fixed V<sub>G</sub> values; (c) impact of V<sub>G</sub> on barrier height and turn-on voltage V<sub>ON</sub>.

FIGURE 6. (a) Waveforms of applied  $V_G$ ,  $V_{BG}$ ,  $V_D$  and light exposure. (b) Evolution of  $I_D$  after light pulses of various intensities.

FIGURE 7. (a) Evolution of hole injection barrier and  $I_{\rm D}$  in the dark and under illumination. (b) Schematic flows of photo-generated electrons and holes.

$I_{OFF}$  state, since  $V_D = 1$  V is too low to overcome the injection barrier built by  $V_G$  pulse. However, as the device is exposed to the light, it turns on after a certain exposure time, see Fig. 6(b).

As the light intensity is increased from 5 to  $20 \mu W/cm^2$ , exposure time to turn on the device falls from 20 to about 5 ms. This indicates that the PD-SOI  $Z^2$ -FET built on PD-SOI substrate is sensitive to the light exposure and can be used for photodetection purpose.

The photoresponse of the  $Z^2$ -FET can be understood by investigating the evolution of hole injection barrier with the exposure time. Figure 7(a) compares the time-dependent hole barriers in the dark and under a light of intensity 5  $\mu$ W/cm<sup>2</sup>. In the dark, the hole barrier is high ( $\sim$ 1.5 V) and does not

change in this short period of time (30 ms), due to the slow thermal generation of electrons. However, under illumination, photo- generated electrons are attracted by the positively biased  $V_G$  and accumulate at the front gate interface, as schematically shown in Fig. 7(b). This gradually reduces the hole injection barrier at the bottom interface due to screening of  $V_G$  by the photoelectrons at the front gate interface. As the hole injection barrier is lowered from 1.5 V to 1 V, the holes from the  $P^+$ -doped drain are injected into the channel and trigger the feedback process. This collapses both barriers and turns on the device sharply, see Fig. 7(a).

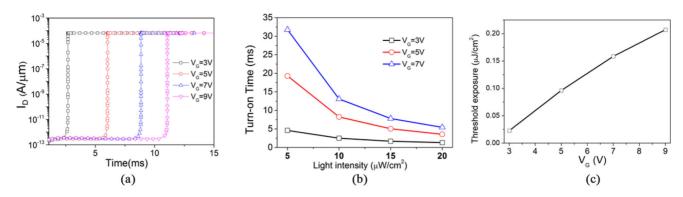

The duration of the exposure that is needed to turn on the device (turn-on time) can be modulated by the  $V_G$ . Higher  $V_G$  induces a taller potential barrier, and thus a longer exposure time is needed to generate enough photoelectrons and turn on the device. This can be observed in Fig. 8(a) where

FIGURE 8. (a) Evolution of I<sub>D</sub> under a fixed light intensity of 15  $\mu$ W/cm<sup>2</sup> and various V<sub>G</sub> from 3 V to 9 V. (b) Relation between exposed light intensity and exposure time to turn on the device as a function of V<sub>G</sub>. (c) Modulation of threshold exposure that triggers the device by applied V<sub>G</sub> under a light intensity of  $5\mu$ W/cm<sup>2</sup>.

the turn-on time increases from about 2.5 ms to about 11 ms as  $V_G$  increases from 3 V to 9 V.

The turn-on time is also modulated by the light intensity, since higher light intensity generates photoelectrons faster and thus shortens the exposure time needed. Figure 8(b) shows the relation between turn-on time and light intensity as a function of  $V_G$ . In fact, it is the exposure that determines the density of generated photoelectrons and thus the turn-on time of the device. Figure 8(c) summarizes the relation between threshold exposure dose needed to turn on the device and the applied  $V_G$  pulse. The threshold exposure increases almost linearly as  $V_G$  increases. Thanks to the sharp switching and high  $I_{ON}$  of the  $Z^2$ -FET, this property might be attractive in application as exposure-triggered switch [29]–[31].

## IV. AN ALTERNATIVE OPERATION MODE

Though the  $Z^2$ -FET used as a sharp switch triggered by a light exposure dose is attractive, in many other applications, such as image sensing, the exposure dose needs to be read out as an output voltage. Conventional CMOS active pixel sensors combine one photodiode with three transistors in order to achieve several functions: photosensing, charge integration, buffer amplification needed to converts the photoelectrons to an output voltage, and random access for sensor array operation. Here, we demonstrate that the  $Z^2$ -FET is actually a single-transistor active pixel sensor (1T-APS), where only one transistor is needed to include all these functions.

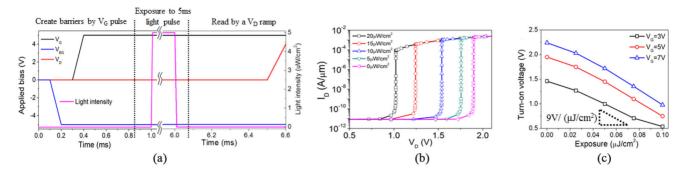

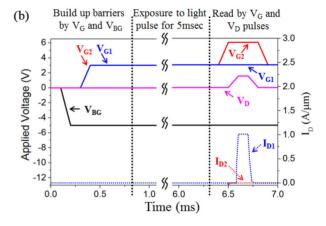

In order to achieve this, an alternative operation mode is developed, where the exposure dose is read out as an output voltage. Figure 9(a) shows the waveforms of the applied bias pulses and the light pulse. Similar to the exposure-triggered switch discussed above,  $V_{BG}$  and  $V_{G}$  pulses are applied sequentially to build up the injection barriers. The device is then exposed to a light pulse of 5 ms duration (simulating the shutter in an image sensor) with light intensity varying from 5 to 20  $\mu$ W/cm<sup>2</sup>. After exposure, a  $V_{D}$  pulse up from 0 to 3 V is applied in order to read out the exposure dose. Figure 9(b) shows the  $I_{D}$ - $V_{D}$  output characteristics of the

device under various illumination conditions. In the dark, a  $V_D \sim 1.8~V$  is needed to turn on the device due to high hole barrier formed by  $V_G = 5~V$  pulse. However,  $V_{ON}$  is markedly reduced after exposure to a light pulse. This is due to the accumulation of photoelectrons under the gate, resulting in a lower potential barrier. The reduction of  $V_{ON}$  with exposure dose is almost linear, see Fig. 9(c). The sensitivity  $S_1$  of the sensor is defined as the change of  $V_{ON}$  with exposure per unit area. It reaches 9 V per  $\mu J/cm^2$  under  $V_G = 3~V$  and increases to 13.4 and 14  $V/(\mu J/cm^2)$  under  $V_G = 5~$  and 7 V, respectively. This sensitivity is higher than that of conventional CMOS sensors, considering the small device area, see Section VIII below. At higher  $V_G$ , the  $V_{ON}$ -exposure curve shifts upward due to higher injection barrier, as shown in Fig. 9(c).

Unlike conventional CMOS active pixel sensors, where additional transistors are used to convert the photoelectrons to an output voltage,  $Z^2$ -FET photodetector converts the light exposure directly to a voltage signal ( $V_{ON}$ ) with high output current. Besides, the  $Z^2$ -FET can achieve random access with the combination of  $V_G$  and  $V_D$  pulses during the read phase, which has been discussed in the context of its DRAM capabilities [32], [33]. Thus, the  $Z^2$ -FET can be used as a one-transistor active pixel sensor, which is more compact than a conventional CMOS sensor.

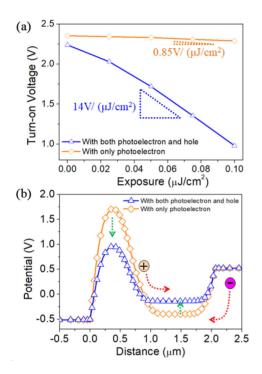

# V. IMPACT OF PHOTO-GENERATED HOLES ON THE SENSITIVITY

Classical image sensors, such charge-coupled as devices (CCDs) and CMOS sensor, employ only photoelectrons, whereas the photo-generated holes are typically discarded. In the Z<sup>2</sup>-FET sensor, the photo-generated holes play a key role. Figure 10(a) compares the relation between exposure rate and V<sub>ON</sub> for two different simulations. Both use  $V_G = 7$  V and other bias values as in Fig. 9(a). In one simulation, both photoelectrons and holes are included, and the sensitivity reaches 14 V/( $\mu$ J/cm<sup>2</sup>). In the other simulations, the holes are ignored, which suppresses the exposure-induced shift of VON and lowers the sensitivity to only 0.85 V/( $\mu$ J/cm<sup>2</sup>).

FIGURE 9. (a) Waveforms of applied bias and light pulses on the  $Z^2$ -FET for the alternative operation mode. (b)  $I_D$ - $V_D$  characteristics during the ramping up of  $V_D$  after exposure to light of various intensities. (c) Relation between turn-on voltage and exposure under various  $V_G$ .

FIGURE 10. (a) Comparison of V<sub>ON</sub>-exposure relations between simulations in which photo-generated holes are or are not included. (b) Comparison of potential profiles between these two cases, and schematic view of photo-generated holes flowing to the intrinsic region and electrons injected out of the N<sup>+</sup>-doped source.

In order to understand this mechanism, potential profiles at the bottom interface are compared in these two cases at t = 6.1 ms after exposure to the light. Apparently, compared to the simulation with photoelectrons only, the device with both photoelectrons and holes shows reduced hole and electron injection barriers, see Fig. 10(b). In fact, the photogenerated holes flow to the intrinsic region and raise its potential. This reduces electron barrier and causes the injection of electrons from the N<sup>+</sup>-doped source into the channel. The electrons then flow to the front-gate interface, as shown in Fig. 10(b).

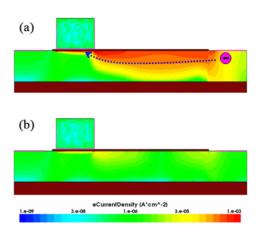

The electron current density has been simulated to confirm this aspect. Figure 11 compares the electron current density extracted at the middle of exposure (t = 3.5 ms) in simulations that do and do not consider the holes.

FIGURE 11. (a) Electron current density considering both photo-generated electron and hole, and (b) that considering only photoelectron.

After electron-hole pair generation, high electron current is observed in Fig. 11(a) flowing from  $N^+$  doped source to the front-gate interface. This markedly reduces the  $V_{ON}$  and thereby leads to high sensitivity. In contrast, in simulations including only electrons, the electron current is very low, see Fig. 11(b).

In fact, the comparison in Fig. 10(a) reveals that photogenerated holes play a more important role than photoelectrons in the operation of the  $Z^2$ -FET photodetector. According to the feedback mechanism in the  $Z^2$ -FET, where hole flows trigger the flow of additional electrons, the photogenerated holes flowing into the source can induce additional electron injection from the N<sup>+</sup>-doped source to the front interface is much stronger than direct electron photogeneration. Thanks to this internal amplification, sensitivity up to 14  $V/(\mu J/cm^2)$  is achieved even with small device area.

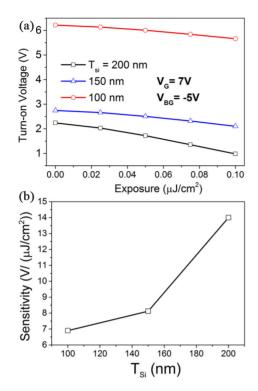

#### VI. IMPACT OF TOP SI THICKNESS ON THE SENSITIVITY

The top Si thickness  $T_{Si}$  has a major impact on the sensitivity of the  $Z^2$ -FET photodetector. Figure 12(a) compares the evolution of  $V_{ON}$  with the exposure dose in devices with three different  $T_{Si}$  values. Apparently, thinner  $T_{si}$  induces higher  $V_{ON}$  and lower sensitivity  $S_1$ . The sensitivity, extracted from the slope in Fig. 12(a), degrades from 14  $V/(\mu J/cm^2)$  down

FIGURE 12. (a) Comparison of Von-exposure relations between devices with three different Tsi values; (b) Sensitivity S1 vs. Tsi.

to 6.8 V/( $\mu$ J/cm<sup>2</sup>) as T<sub>Si</sub> is reduced from 200 to 100 nm, see Fig. 12(b).

The dynamic coupling effect and screening by photo- generated electrons also occur in an FD-SOI Z<sup>2</sup>-FET, as seen in the  $T_{Si} = 100$  nm curves in Fig. 12(a). However, due to the thin top Si layer, the sensitivity is reduced. The degradation of sensitivity with thin Si layer is due to the poor absorption of light in the thin TSi. Thus, a PD-SOI structure with relatively thick Tsi is preferable, in which the dynamic coupling effect is the dominant mechanism, as discussed in Section II. However, a Tsi that is too thick decreases Von due to weak coupling, and reduces the dynamic range of the detector, see Fig. 12(a).

#### **VII. OPERATION OF SENSOR ARRAY**

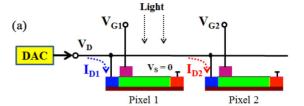

A conventional CMOS APS normally combines one photodiode and three transistors in order to perform photosensing, charge integration, amplification and enable random pixel access [34], [35]. Thus, conventional CMOS sensors have a complicated pixel architecture design and low quantum efficiency. However, the Z<sup>2</sup>-FET naturally has random access capability, as discussed in its DRAM application [32], [33].

Figure 13(a) shows the architecture of our proposed  $\mathbb{Z}^2$ -FET detector array. A  $1\times2$  array is simulated to emulate sensors in the same row. Since pixels in the same row share the same V<sub>D</sub> signal, the random access of a certain pixel can only be achieved by using V<sub>G</sub> to select a certain column. Figure 13(b) shows the applied voltage waveforms and the drain currents of the two pixels. As in Fig. 9(a), V<sub>BG</sub> is

FIGURE 13. (a) Schematic diagram of a proposed Z<sup>2</sup>-FET APS array; (b) TCAD simulation of a  $1 \times 2$   $Z^2$ -FET array, including readout waveforms.

pulsed from zero down to -5~V, followed by  $V_{\rm G1}$  and  $V_{\rm G2}$ both pulsed from zero up to 3 V to build up barriers in both pixels. Then, only pixel 1 is exposed to a light pulse for 5 ms, whereas pixel 2 is kept in the dark. After exposure, in order to read photoelectrons accumulating in pixel 1 without affecting pixel 2, the V<sub>G2</sub> rises up to 6 V and V<sub>G1</sub> is kept at 3V. Thus, the potential barrier in pixel 2 is raised, which keeps the pixel 2 in I<sub>OFF</sub> state during the readout operation by the V<sub>D</sub> pulse. As V<sub>D</sub> is pulsed from zero to 1.5 V, it only turns on pixel 1 in which V<sub>ON</sub> has been shifted by the light exposure, see Fig. 13(b).

## VIII. DISCUSSION

Compared to conventional CMOS sensors, the Z<sup>2</sup>-FET-based APS has two unique advantages:

- 1) As demonstrated in Fig. 13, Z<sup>2</sup>-FET integrates all functions, including photosensing, charge integration, amplification and random access in one transistor, and thus it is a true one-transistor APS. Thus it is more compact and design-friendly than conventional CMOS sensors.

- 2) Thanks to its near-zero SS, the Z<sup>2</sup>-FET turns on sharply from I<sub>OFF</sub> to I<sub>ON</sub> and has a well-defined turn-on voltage V<sub>ON</sub>. The exposure of the sensor can be directly read out by measuring V<sub>ON</sub>. This can be achieved by using a digitalto-analog converter (DAC) to scan the V<sub>D</sub> and register the digital value of V<sub>D</sub> as the device is turned on, as shown schematically in Fig. 13(a). In a standard CMOS sensor, the output voltage is converted to a digital value by an analog-to-digital converter (ADC). Conventionally, design of high-performance DAC is easier than that of ADC.

The performance of the Z<sup>2</sup>-FET photodetector obtained in our simulations is compared with conventional CMOS

| TABLE 1.     | Performance      | comparison | between | Z <sup>2</sup> -FET | and | other | CMOS |

|--------------|------------------|------------|---------|---------------------|-----|-------|------|

| sensors from | n literature [35 | 5]−[38].   |         |                     |     |       |      |

| Parameter               | Ref<br>[35] | Ref<br>[36] | Ref [37] | Ref<br>[38] | This<br>work |  |

|-------------------------|-------------|-------------|----------|-------------|--------------|--|

| Pixel area (μm²)        | 34.3        | 1.25        | 30.25    | 2.04        | 2.2          |  |

| Sensitivity (e-/lux·s)  | 17,500      | 6,700       | /        | 7922        | 180,000      |  |

| Conversion gain (µV/e-) | 30.3        | 63.2        | 20       | 76.6        | 19.4         |  |

| Full well capacity (e-) | 30,500      | 5000        | 25,000   | 9700        | 32,000       |  |

| Operating voltage       | 3.3 V       | 2.7 V       | 3.3 V    | 2.9 V       | 3 V          |  |

sensors [35]–[38] collected in Table 1. The performance parameters of  $Z^2$ -FET photodetector were calculated using the device area of 2.2  $\mu m^2$ . From Fig. 9(c) we find the sensitivity of  $Z^2$ -FET to be  $S_1 = 9 \text{ V/}(\mu \text{J/cm}^2)$  at  $V_G = 3 \text{ V}$ . This can be converted into a CMOS-sensor sensitivity S in units of e-/(lux·s), defined as the number of photoelectrons that accumulate under the front gate due to 1 lux.s exposure, via:

$$S = \frac{S_1 \times C_{ox}}{R \times q},\tag{1}$$

where  $C_{ox}$  is the capacitance of the front gate capacitor, q is the electron charge, and R is the ratio between  $V_{ON}$  and  $V_{G}$ , which is 0.22 according to Fig. 5(c). This leads to  $S=1.8\times10^5$  e-/(lux·s), much higher than conventional CMOS sensors, see Table 1. The high sensitivity originates from the feedback process, where the photo-generated holes trigger high electron injection as discussed in Section V.

The conversion gain G, which indicates the change in  $V_{ON}$  per photoelectron, is given by the ratio of  $S_1/S$ . We obtain  $G=19.4~\mu\text{V/e-}$ , comparable to other CMOS sensors. Finally, the full well capacity (FWC), which determines the dynamic range of the sensor, can be estimated via:

$$FWC = \frac{V_G \times C_{ox}}{q}.$$

(2)

The FWC of  $Z^2$ -FET reaches 32000 electrons under  $V_G =$  3 V, which is also comparable with other CMOS sensors.

#### IX. CONCLUSION

In this work, we have explored the dynamic coupling effect in the  $Z^2$ -FET built in PD-SOI substrate, which helps to rebuild the potential barriers and restore the sharp switching characteristics. This effect has further been used for photodetection, where photoelectrons accumulating at the top interface screen front gate control of the bottom interface of the channel. This reduces the hole injection barrier and triggers the device after a certain exposure. An alternative operation mode has been explored in which the exposure is directly converted to a turn-on voltage without the need

for additional transistors. Unlike conventional image sensors, photo-generated holes are critical in the  $Z^2$ -FET sensor, inducing more electron accumulation and achieving sensitivity of up to  $S=1.8\times 10^5$  e-/(lux·s) With high sensitivity and one-transistor compact cell architecture, the  $Z^2$ -FET is very promising for photodetection and image sensing applications.

#### **REFERENCES**

- H. Cai, Y. Wang, L. A. De Barros Naviner, and W. Zhao, "Robust ultra-low power non-volatile logic-in-memory circuits in FD-SOI technology," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 64, no. 4, pp. 847–857, Apr. 2017.

- [2] B. Pelloux-Prayer et al., "Fine grain multi-V<sub>T</sub> co-integration methodology in UTBB FD-SOI technology," in Proc. IFIP/IEEE 21st Int. Conf. Very Large Scale Integr. (VLSI-SoC), Istanbul, Turkey, 2013, pp. 168–173.

- [3] R. Taco, I. Levi, M. Lanuzza, and A. Fish, "Low voltage logic circuits exploiting gate level dynamic body biasing in 28 nm UTBB FD-SOI," *Solid-State Electron.*, vol. 117, pp. 185–192, Mar. 2016.

- [4] P. Magarshack, P. Flatresse, and G. Cesana, "UTBB FD-SOI: A process/design symbiosis for breakthrough energy-efficiency," in Proc. Design Autom. Test Europe (DATE), Grenoble, France, 2013, pp. 952–957.

- [5] M. S. Parihar et al., "Insight into carrier lifetime impact on band-modulation devices," Solid-State Electron., vol. 143, pp. 41–48, May 2018.

- [6] C. Fenouillet-Beranger et al., "Hybrid FDSOI/bulk high-k/metal gate platform for low power (LP) multimedia technology," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Baltimore, MD, USA, 2009, pp. 1–4.

- [7] M. S. Dahlem et al., "Electronic-photonic integrated circuits in siliconon-insulator platforms," in Proc. 30th URSI Gen. Assembly Sci. Symp., Istanbul, Turkey, 2011, p. 1.

- [8] D. A. B. Miller, "Device requirements for optical interconnects to silicon chips," *Proc. IEEE*, vol. 97, no. 7, pp. 1166–1185, Jul. 2009.

- [9] A. H. Atabaki *et al.*, "Integrating photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349–354, 2018.

- [10] M. Mansoor, I. Haneef, S. Akhtar, M. A. Rafiq, S. Z. Ali, and F. Udrea, "SOI CMOS multi-sensors MEMS chip for aerospace applications," in *Proc. IEEE Sensors*, Valencia, Spain, 2014, pp. 1204–1207.

- [11] M. A. Marwick and A. G. Andreou, "A UV photodetector with internal gain fabricated in silicon-on-sapphire CMOS," in *Proc. IEEE Sensors*, Atlanta, GA, USA, 2007, pp. 535–538.

- [12] C. Novo, R. Buhler, J. Baptista, R. Giacomini, A. Afzalian, and D. Flandre, "Quantum efficiency improvement of SOI p-i-n lateral diodes operating as UV detectors at high temperatures," *IEEE Sensors* J., vol. 17, no. 6, pp. 1641–1648, Mar. 2017.

- [13] G. Li et al., "Multiple-wavelength detection in SOI lateral PIN diodes with backside reflectors," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7368–7376, Sep. 2017.

- [14] G. Li et al., "Operation of suspended lateral SOI PIN photodiode with aluminum back gate," in Proc. Joint Int. EUROSOI Workshop Int. Conf. Ultimate Integr. Silicon (EUROSOI-ULIS), Vienna, Austria, 2016, pp. 155–158.

- [15] G. Li, K. Maekita, H. Mitsuno, T. Maruyama, and K. Iiyama, "Over 10 GHz lateral silicon photodetector fabricated on silicon-on-insulator substrate by CMOS-compatible process," *Jpn. J. Appl. Phys.*, vol. 54, no. 4S, 2015, Art. no. 04DG06.

- [16] L. Kadura et al., "Extending the functionality of FDSOI N- and P-FETs to light sensing," in Proc. IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2016, pp. 32.6.1–32.6.4.

- [17] L. Grenouillet et al., "Smart co-integration of light sensitive layers with FDSOI transistors for more than Moore applications," in Proc. SOI-3D-Subthreshold Microelectron. Technol. Unified Conf. (S3S), Millbrae, CA, USA, 2014, pp. 1–2.

- [18] J. N. Deng et al., "Interface coupled photodetector (ICPD) with high photoresponsivity based on silicon-on-insulator substrate (SOI)," *IEEE J. Electron Devices Soc.*, vol. 6, no. 1, pp. 557–564, Jan. 2018.

- [19] J. Wan, S. Cristoloveanu, C. Le Royer, and A. Zaslavsky, "Z<sup>2</sup>-FET field-effect transistor with a vertical subthreshold slope and with no impact ionization," U.S. Patent 8581310B2, 2013.

- [20] C. Navarro et al., "Z<sup>2</sup>-FET as capacitor-less eDRAM cell for high-density integration," *IEEE Trans. Electron Devices*, vol. 64, no. 12, pp. 4904–4909, Dec. 2017.

- [21] J. Wan, S. Cristoloveanu, C. Le Royer, and A. Zaslavsky, "A feedback silicon-on-insulator steep switching device with gate-controlled carrier injection," *Solid-State Electron.*, vol. 76, pp. 109–111, Oct. 2012.

- [22] Y. Solaro et al., "Z<sup>2</sup>-FET: A promising FDSOI device for ESD protection," Solid-State Electron., vol. 97, pp. 23–29, Jul. 2014.

- [23] P. Fonteneau, Y. Solaro, D. Marin-Cudraz, C.-A. Legrand, and C. Fenouillet-Beranger, "Innovative high-density ESD protection device in state of the art UTBB FDSOI technologies," in *Proc. 37th Elect. Overstress Electrostatic Discharge Symp. (EOS/ESD)*, 2015, pp. 1–7.

- [24] S. Cristoloveanu *et al.*, "A review of the Z<sup>2</sup>-FET 1T-DRAM memory: Operation mechanisms and key parameters," *Solid-State Electron.*, vol. 143, pp. 10–19, May 2018.

- [25] H. El Dirani et al., "Ultra-low power 1T-DRAM in FDSOI technology," Microelectron. Eng., vol. 178, pp. 245–249, Jun. 2017.

- [26] S.-M. Joe, H.-J. Kang, N. Choi, M. Kang, B.-G. Park, and J.-H. Lee, "Diode-type NAND flash memory cell string having super-steep switching slope based on positive feedback," *IEEE Trans. Electron Devices*, vol. 63, no. 4, pp. 1533–1538, Apr. 2016.

- [27] M. Bawedin, S. Cristoloveanu, J. G. Yun, and D. Flandre, "A new memory effect (MSD) in fully depleted SOI MOSFETs," *Solid-State Electron.*, vol. 49, no. 9, pp. 1547–1555, 2005.

- [28] J. Chu, Z. Han, F. Meng, and Z. Wang, "Spectral response of blue-sensitive Si photodetectors in SOI," *Solid-State Electron.*, vol. 55, no. 1, pp. 54–58, 2011.

- [29] Y.-J. Heo et al., "Semiconductor-type auto-exposure control sensor with a Schottky barrier for radiography application," Sci. Adv. Mater., vol. 9, no. 8, pp. 1329–1333, 2017.

- [30] M. Söderberg and M. Gunnarsson, "Automatic exposure control in computed tomography—An evaluation of systems from different manufacturers," *Acta Radiologica*, vol. 51, no. 6, pp. 625–634, 2010

- [31] S. Pan and X. An, "Content-based auto exposure control for on-board CMOS camera," in *Proc. 11th Int. IEEE Conf. Intell. Transport. Syst.*, Beijing, China, 2008, pp. 772–777.

- [32] J. Wan, C. L. Royer, A. Zaslavsky, and S. Cristoloveanu, "A compact capacitor-less high-speed DRAM using field effect-controlled charge regeneration," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 179–181, Feb. 2012.

- [33] M. S. Parihar et al., "Low-power Z<sup>2</sup>-FET capacitorless 1T-DRAM," in Proc. IEEE Int. Memory Workshop (IMW), Monterey, CA, USA, 2017, pp. 1–4.

- [34] M. Bigas, E. Cabruja, J. Forest, and J. Salvi, "Review of CMOS image sensors," *Microelectron. J.*, vol. 37, no. 5, pp. 433–451, 2006

- [35] Y. Oike et al., "An 8.3M-pixel 480fps global-shutter CMOS image sensor with gain-adaptive column ADCs and 2-on-1 stacked device structure," in *Proc. VLSI Circuits*, Honolulu, HI, USA, 2016, pp. 1–2.

- [36] S. Sukegawa et al., "A 1/4-inch 8Mpixel back-illuminated stacked CMOS image sensor," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, USA, 2013, pp. 484–485.

- [37] Y. Oike and A. E. Gamal, "CMOS image sensor with per-column ΣΔ ADC and programmable compressed sensing," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 318–328, Jan. 2013.

- [38] A. Suzuki et al., "6.1 A 1/1.7-inch 20Mpixel back-illuminated stacked CMOS image sensor for new imaging applications," in Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC), San Francisco, CA, USA, 2015, pp. 110–111.